国产FPGA概况

时至今日,不管从国际形势还是国家对于“中国芯”的扶持,“国产化”这一话题越来越要付出实践,对于FPGA这一“万能芯”也是很多企业会优先考虑的。

从华为被“卡脖子”到集成电路正式成为国家学科,都能看出国家对于国产芯的迫切发展,今天就来简单总结下国产FPGA这一“万能芯”的发展概况。

西安智多晶微电子有限公司,成立于2012年,总部位于西安,北京设立有EDA软件研究中心。创始团队拥有三十多年丰富的FPGA设计制造经验,曾就职于海外该领域领先企业,并担任多个专业方向技术带头人。核心团队来自于国内各知名院校和优秀的FPGA研发团队,是国内目前集硬软件设计、生产、销售最具竞争力的高科技企业。公司专注可编程逻辑电路器件技术的研发,并为系统制造商提供高集成度、高性价比的可编程逻辑器件、可编程逻辑器件IP核、相关软件设计工具以及系统解决方案。赋能产业,“芯”系未来,是智多晶的奋斗愿景,团队致力于在LED驱动、视频监控、图像处理、工业控制、4G/5G通信网络、数据中心等各行业应用充分发挥FPGA的方案优势,以市场和客户为导向,帮助合作伙伴提升其核心竞争力。公司目前已实现55nm、40nm工艺中密度FPGA的量产,并针对性推出了内嵌Flash、SDRAM等集成化方案产品,截至2018年已批量发货2KK片。通过严谨科学的设计,360度围绕客户的技术支持及服务,以及贯穿全流程的高标准测试管理,我们正在为更多的行业合作伙伴提供最符合需求的高性价比FPGA整体解决方案。

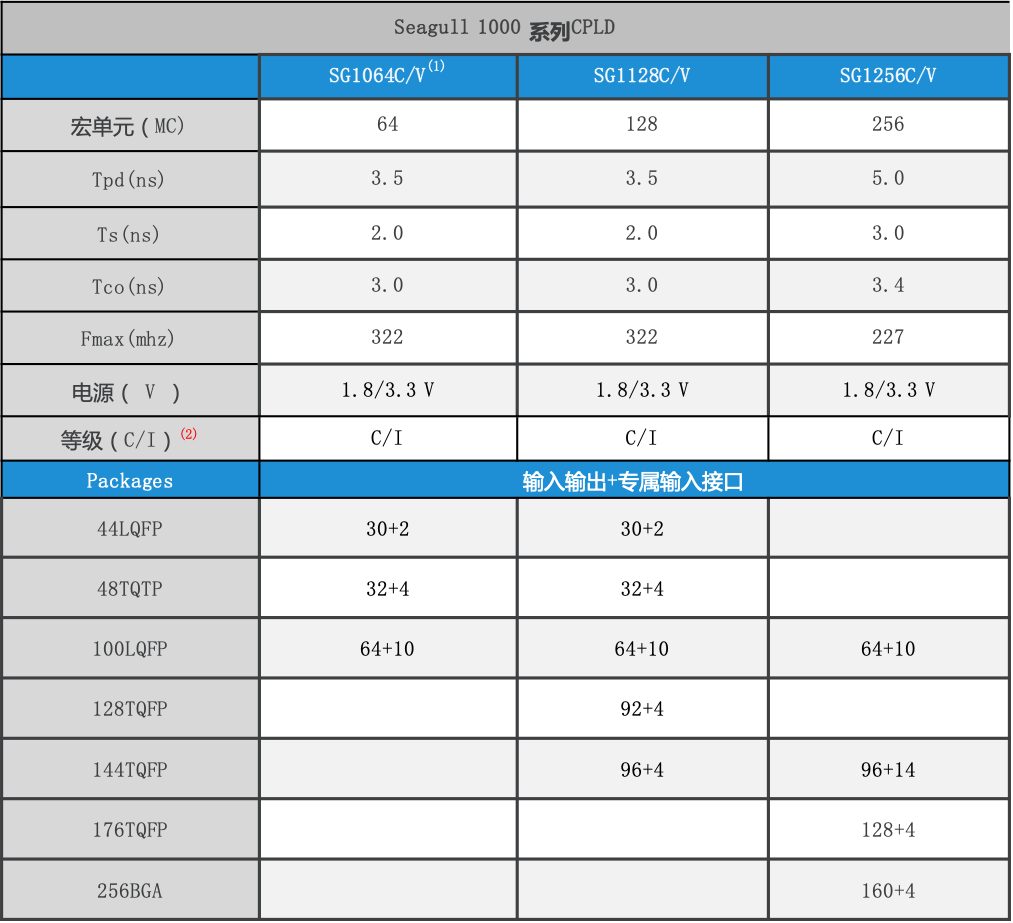

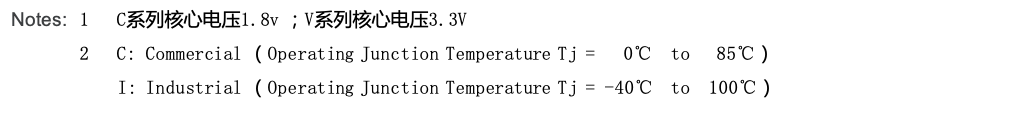

1.2.1 Seagull 1000 系列CPLD产品特性 ● 采用0.162um的低功耗技术工艺,正向自主研发的构架设计,提供64-256宏单元阵列产品● 采用先进的嵌入式闪存(eFlash)的低功耗存储单元,具备数据加密功能● 最大频率Fmax=322MHz,3.5ns快速输入输出(I/O)引脚延迟● 每个输出可高达80 PTs,高达四个总体OE控制,四个专用总体时钟输入接口,每个宏单元都具备时钟、输出、使能设置/复位智能控制组合及在功能模块间共享● 丰富输入资源(36输入逻辑块),提供状态机及计数器设计,个别地方OE控制每个I/O引脚● 核心操作电源为3.3V和1.8V,使用符合IEEE 1532接口的3.3V/1.8V 在系统可编程(In-System Programmable,ISP)● 低功耗:静态电流1.0mA @1.8V,是功耗敏感的应用的最佳解决器件● 多功能可编程输入输出接口 ,支持3.3V, 2.5V or 1.8V I/O电源1.2.2 Sealion 2000 系列FPGA产品特性● 采用55nm的低功耗技术工艺,正向自主研发,先进的低成本、低功耗FPGA架构 提供4K到25K的查找表逻辑单元,单一封装集成了2M*32 bit Synchronous DRAM(SDRAM) 嵌入式高速双接口存储器(dual port SRAM/FIFO Block )(真双端/伪双端) 内置多个18×18/9×9可串行乘法器以及算术逻辑单元(ALU),可做两层叠加实现DSP处理的应用● 内置2个锁相环(PLL)和2个延时锁相环(DLL),提供倍频、分频、相位转移等系统时钟功能● 通用输入输出端口支持高速存储器界面, DDR、DDR2 支持 400Mbps DDR2界面,DQS 输入端90 度相位转换 DQS输入端到系统时钟接轨(clock domain transfer),1:4 and 4:1 串行并行转换(Serializer / Deserializer)● 通用输入输出端口,支持800Mbps LVDS 支持低压差分信号传输接口(LVDS)800Mbps● 芯片性能能够与Spartan-6/Cyclone-4系列的FPGA芯片相匹配1.2.3 Seal 5000 系列 FPGA概述Seal 5000 FPGA同样采用正向设计,芯片软件设计流程和ISE/Quartus II/Diamond 类似,包括综合、约束、布局布线、下载编程等。智多晶的芯片使用自主研发的FPGA开发软件“HqFpga”, 完成综合、布局布线、时序分析、配置编程和片内逻辑分析。智多晶的Seal 5000系列FPGA芯片,在性能上能够与Virtex-7系列的FPGA芯片对标。 Seal 5000 系列FPGA为高性能逻辑设计人员、高性能DSP设计人员和高性能嵌入式系统设计人员提供了满足逻辑、DSP、软/ 硬微处理器和连接功能的需求的最佳解决方案。 基于28纳米技术工艺(28nm),20K到200K的查找表逻辑单元 嵌入式高速双接口存储器(dual port SRAM/FIFO Block)(真双端/伪双端) 内置多个with pre-adder 18×18/9×9可串行乘法器以及算术逻辑单元(ALU),可做两层叠加实现DSP处理的应用,频率高达500MHZ。● 内置锁相环(PLL)提供倍频、分频、相位转移、spread spectrum等系统时钟功能● 通用输入输出端口支持高速存储器界面,SDR、DDR2、DDR3、LPDDR2、LPDDR3 支持 1.2Gbps DDR3界面,DQS 输入端90 度相位转换 DQS输入端到系统时钟接轨(clock domain transfer),1:4 and 4:1 串行并行转换(Serializer / Deserializer)● 通用输入输出端口,支持1.2 Gbps LVDS 支持低压差分信号传输接口(LVDS)1.2Gbps 4个通道的嵌入式 SERDES 支持 6Gbps 全双工串行( full-duplex )协议 内置物理编码子层(Physical Coding Sublayer 、PCS) 支持常用的数据协议,包括PCI Express、千兆以太网(GbE, SGMII)、XAUI、SRIO、CPRI、 OBSAI、SD-SDI 和HD-SDI.

我在官网没找到相关的EDA软件和License介绍,但是在北京飘石科技有限公司(两家公司关系下面会介绍)提供了下载链接和评估版本,但是不清楚为什么不在自己官网集成或者添加链接。

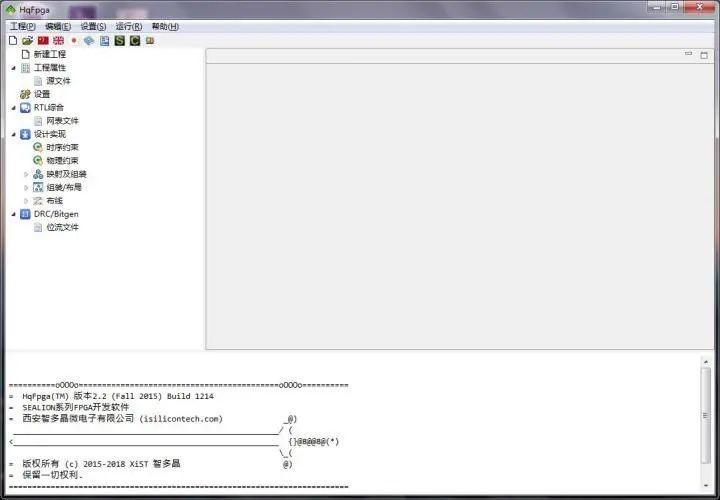

下面开始使用一下HqFPGA。

有了自家的FPGA,没有自己的综合工具怎么办,那也没人愿意使用啊。智多晶找到了国内一家专业做FPGA综合工具的公司---北京飘石科技有限公司,然后建立合作。在我实习期间,该公司已和智多晶商洽并购事宜,目前从飘石官网来看,产品没有更新了,估计已经被智多晶拿下了,成为智多晶不可分割的一部分。智多晶FPGA综合工具名为HqFpgaXIST,我们自己称为HQ。

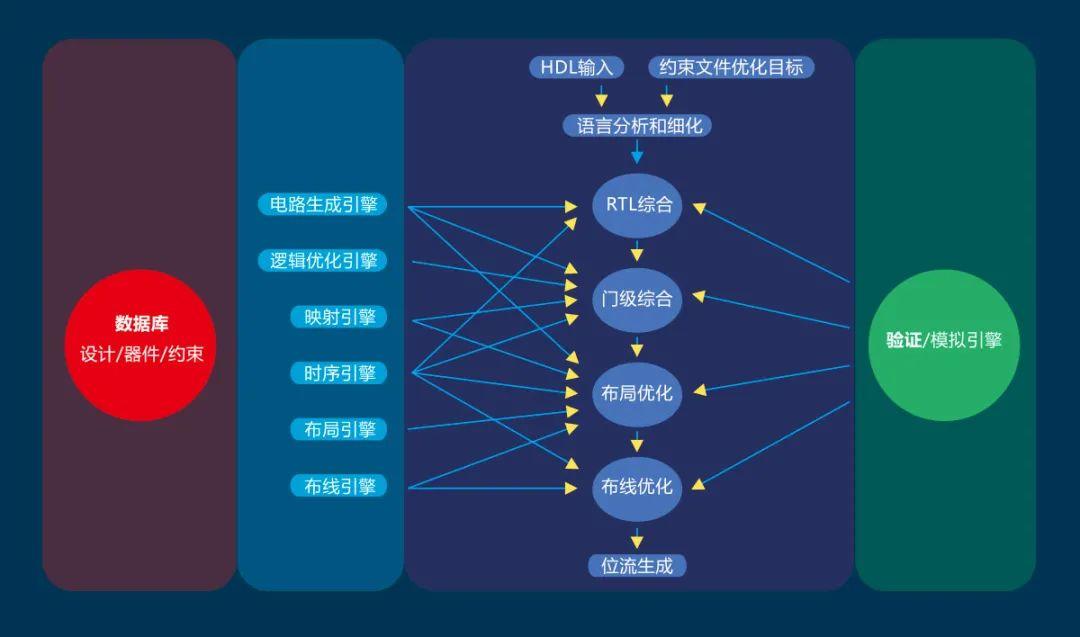

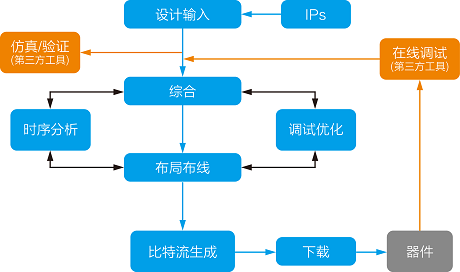

国内外大多数FPGA软件是单点工具的堆集,虽然这些单点工具也“集成”在一个软件系统中,但工具之间只能通过文件接口来传递设计信息,造成工作重复、运行时间长、一致性差、无法全局优化等问题。HqFpga在单一的可执行文件中集成了RTL-to-FPGA的所有功能。各功能模块共享统一的数据模型、器件模型及时序分析引擎,从而得以完成简单、快速、高效及优化的FPGA开发。

1.FPGA 资源感知综合(Resource Aware Synthesis)●时钟感知布局(Clockaware placement)

当然有些功能是刚做出来,只能达到功能实现,还没有很好的交互,比如Insight(该功能类似于逻辑分析仪,完全自主开发,不是像quartus的signaltap是从综合网表级抓取信号,而是直接在RTL级抓取信号)目前用于简单调试可行,太庞大的工程还不能很好的支持。

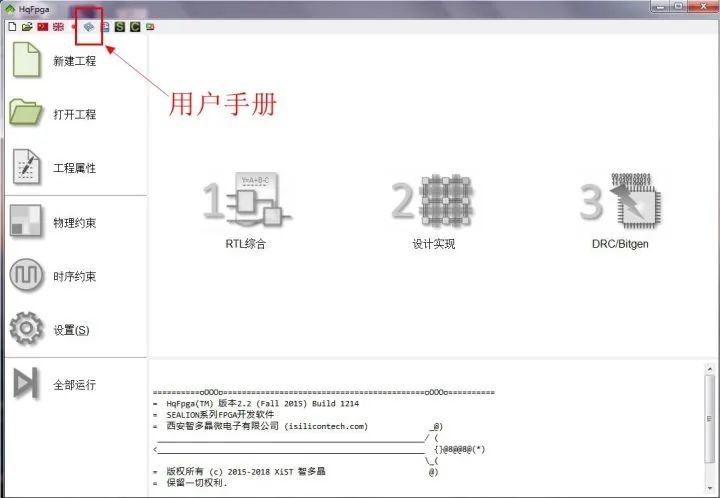

还可以是这样的。HQ支持两种界面,前图为标准界面,也就是默认界面,你点击左上方“C”按钮即可切换为后图传统视图风格,你喜欢怎样就怎样,个人比较喜欢第一种标准视图风格,简洁干净,主视图区三个大大的标志从左往右走完,即可完成从RTL--->bitstream(下载文件)的全过程。同时支持脚本操作,是标准的tcl,这个在FPGA开发的时候真是良心设计(给赞了)。

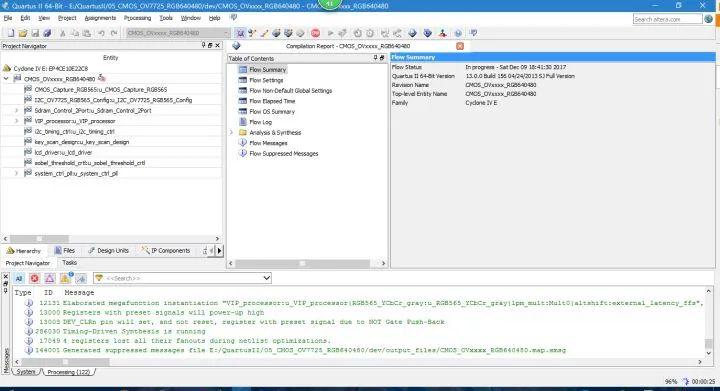

说到综合器,必然会考虑其性能,尤其是编译速度,毕竟像vivado这样的巨无霸等起来都可以来局王者农药了。我这里拿我做过的一个摄像头+VGA+LCD的工程来测试一下。具体软件操作这里不做详细介绍,可以从下图所示位置查看用户手册,比较全面,尤其是命令方式操作。

先上几幅图来感受一下软件的风格,您肯定会觉得和市面上各大佬的风格完全不同。

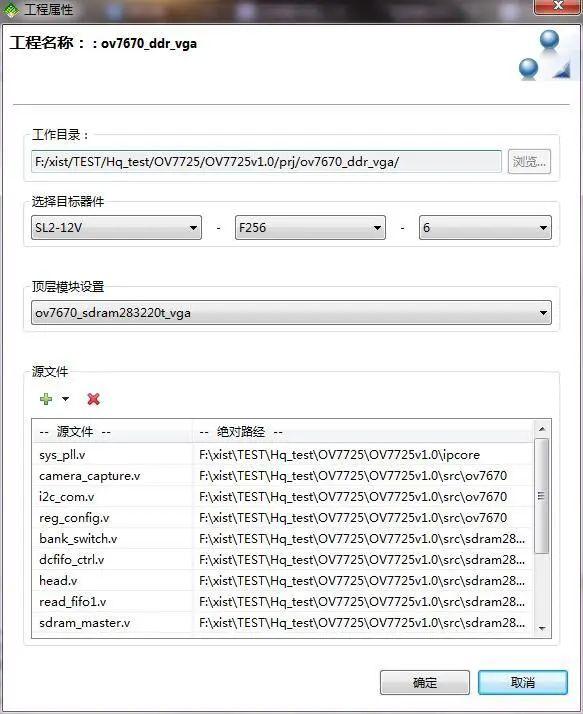

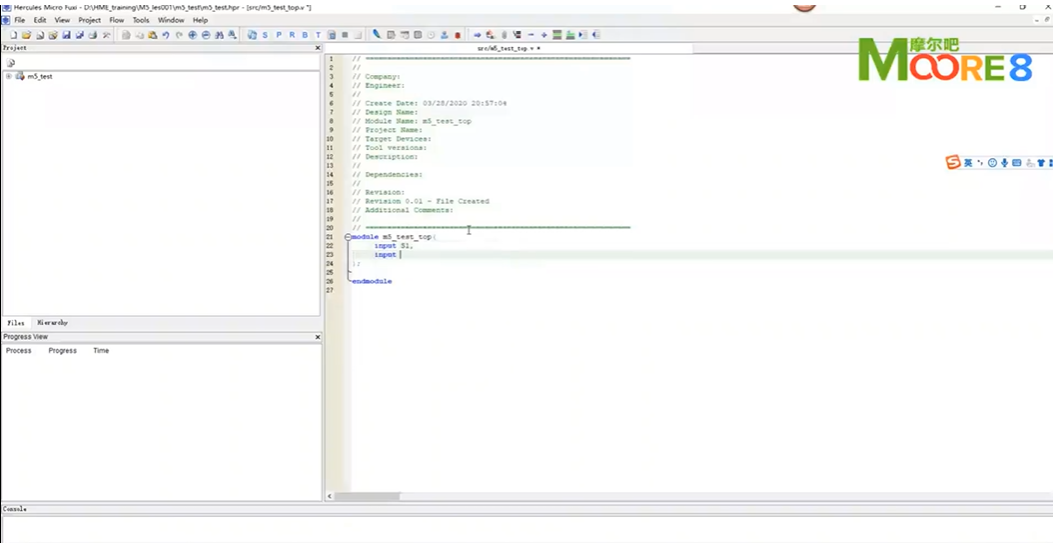

新建工程后,是这样添加源文件的。新建工程的时候需要选择具体哪一款FPGA。

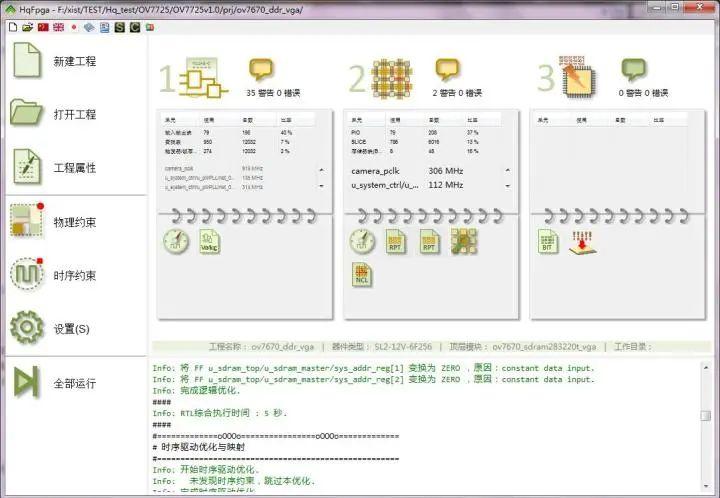

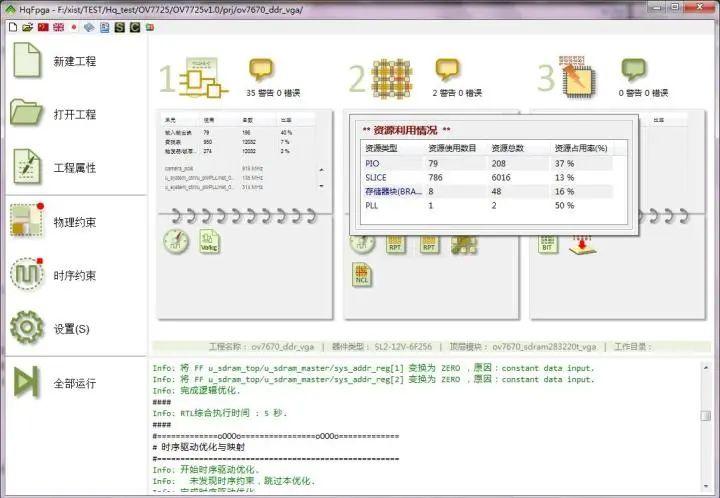

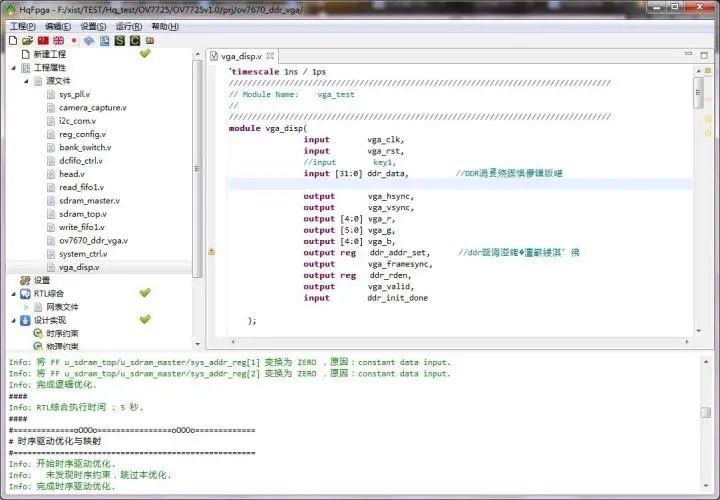

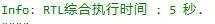

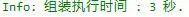

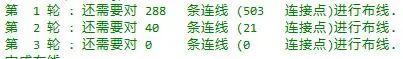

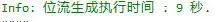

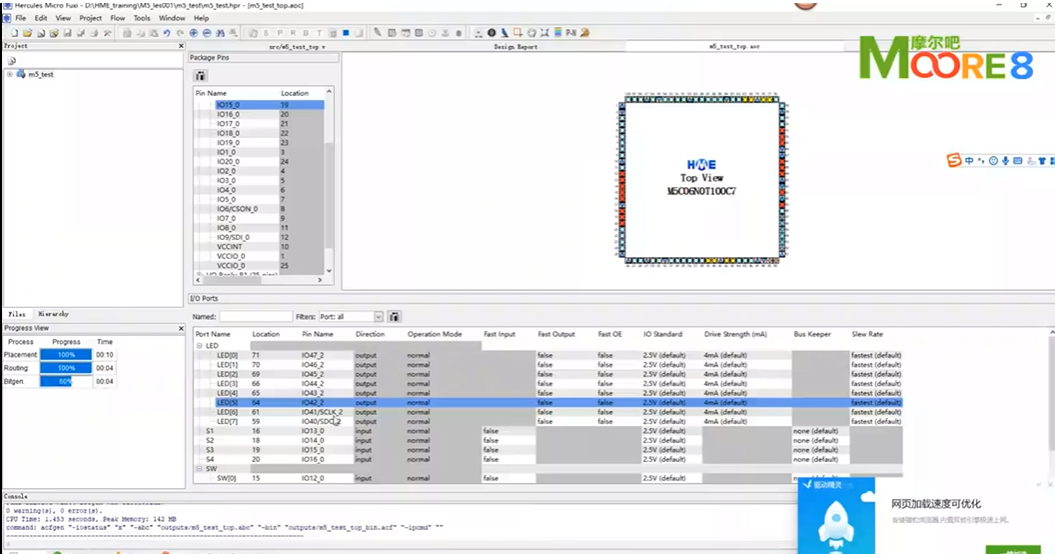

工程文件添加好以后,以此点击点击工作区的那三个大按钮,就可以完成编译和综合工作。在主视图去下方可以看到编译信息。如果有错误同样会提示,只不过目前不是很完善,无法双击错误提示信息进行定位,但是提供了行号,也比较方便。可以通过点击主视图区中小按钮进行信息查看。

比如综合信息查看,还可以在工程文件夹下找到该记录文件。

比如时序约束文件的建立或导入,时序约束文件是标准的.sdc文件。

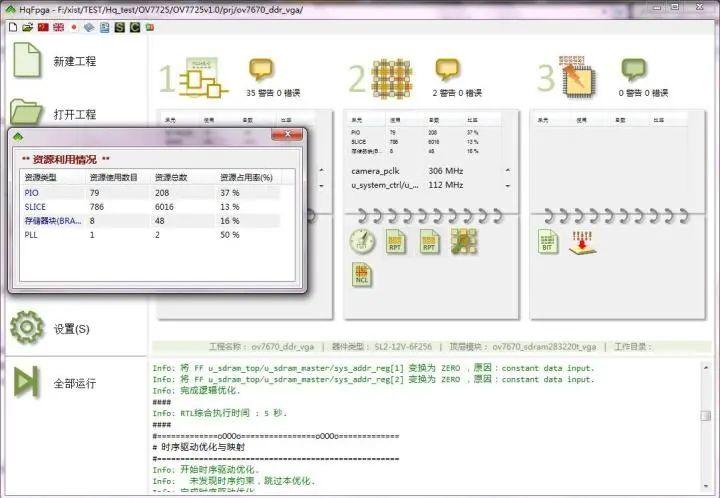

比如资源利用查看。

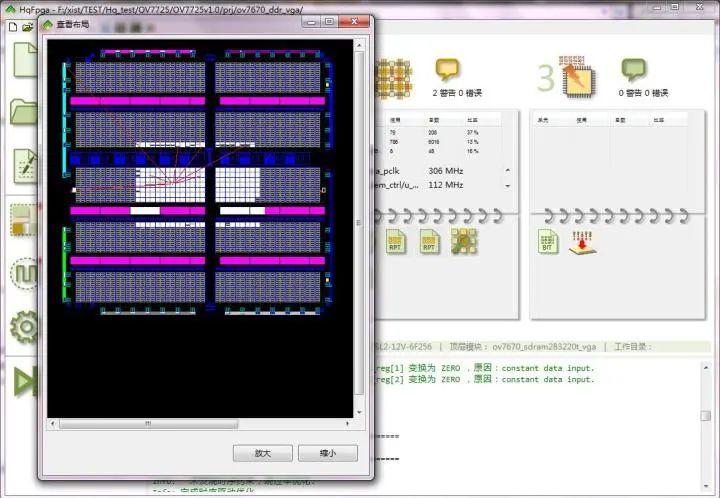

比如布局情况查看,可放大缩小,使用和quartus的差不多,不过HQ更简洁,也意味着功能还不是能强大,比如没有逻辑锁定功能。

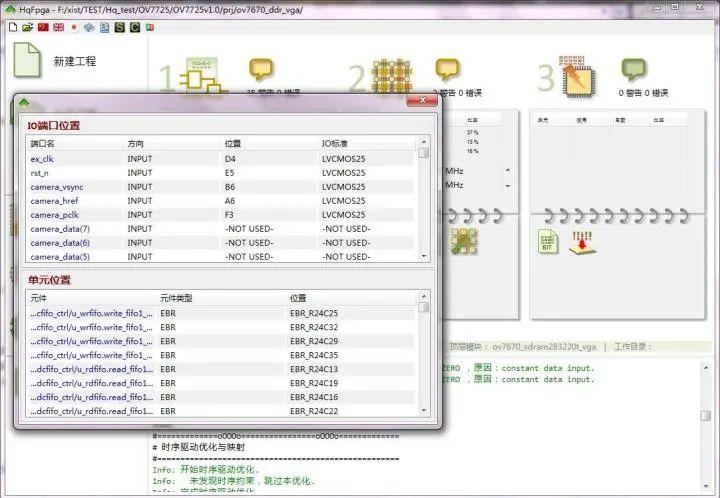

比如综合后个单元位置信息。

比如资源利用统计简报。

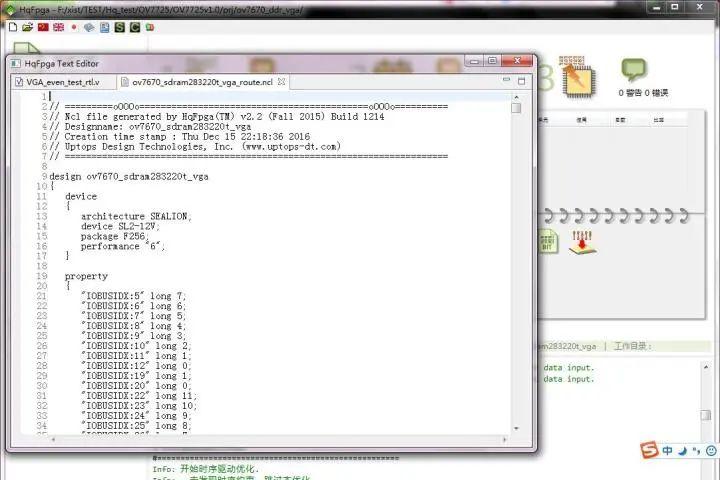

比如综合后生成的ncl网表文件,直接可以查看,尤其是在时序过不去的时候,需要手动布局可以用这个文件。最后就是生产比特流,作为下载文件。目前下载文件格式是.svf。该版本HQ还不能支持下载,需要ispLEVER中的SVFdebug插件进行文件下载。

这是在传统视图模式下的情况,和普通工具类软件差不多,左边工程目录,右边编辑区。标准和传统两种视图可以任意切换,溜溜的。

看了这么多图片,相信您已经感觉到了HQ和别家综合器的不同之处了,那么HQ性能如何呢?我们可以查看综合信息来一探究竟。

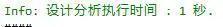

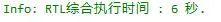

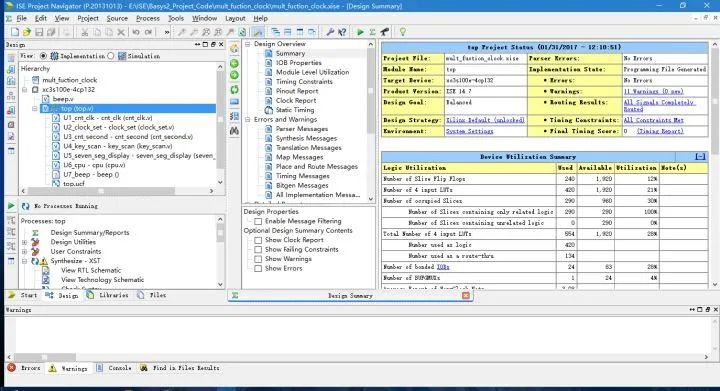

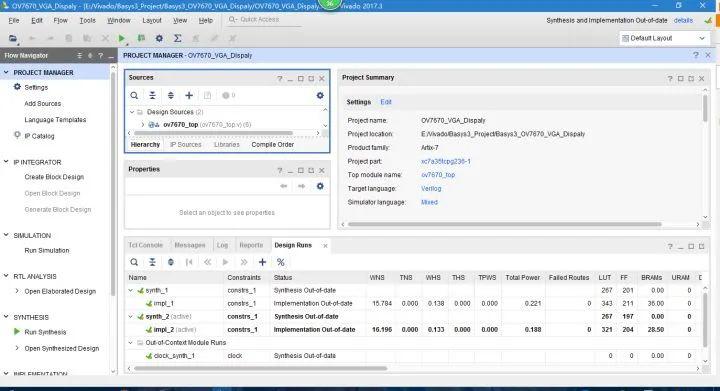

从上图可以看到这个过程只花费了67s就生成了比特流下载文件,我的笔记本是i3处理器,用了5年了,反正很卡。那么这个表现到底怎么样呢?由于HQ还不是很完善,尤其是调试部分的功能,所以在做这个工程之前是用altera的cyclone4进行实现,然后移植到智多晶的FPGA上,幸好这个工程还没有删除,所以我用quartus进行综合,看看二者的差别。

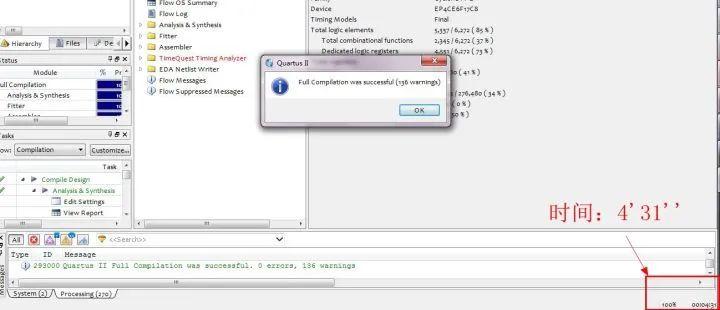

不知道图片右下角的时间您能不能看清,我专门标注了,4分31秒。HQ用的时间67秒,是quartus的1/4,这个数据可能和电脑有很大关系,但是我是在同一台机子上做的测试,所以比较可信。

这或许是因为HQ现在还有一些功能不具备,导致其综合速度完胜quartus。但是也有一些必然因素。我在实习期有幸和飘石公司的技术大拿因为项目交流过,他主要负责HQ中bitstream的生成,从他那里了解到HQ所用的布局布线的算法以及下载文件生成的算法和ISE、vivado、quartus、diamond以及synplify(综合部分算法)不同,具体有哪些不同我也不清楚,毕竟综合器里面全是算法密集区,但是可以通过HQ综合过程的打印信息可以大概知道RTL到bitstream这个过程经历了哪些环节,十分详细,如果您有兴趣可以仔细研究,包括HQ综合后的时序报告,个人觉得比Timequest好用很多,并且时序报告很直观。

2.1 公司简介

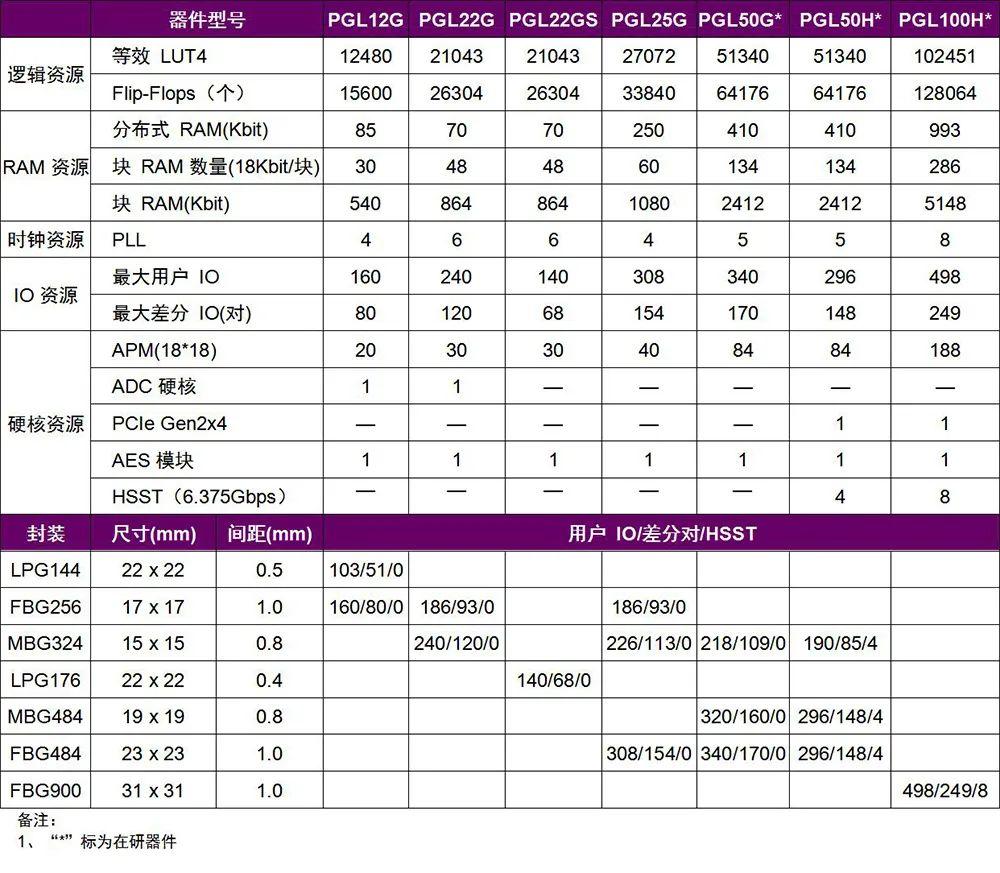

深圳市紫光同创电子有限公司,系紫光集团下属公司,专业从事可编程逻辑器件(FPGA、CPLD等)研发与生产销售,是中国FPGA领导厂商,致力于为客户提供完善的、具有自主知识产权的可编程逻辑器件平台和系统解决方案。紫光同创注册资本4亿元,总投资超过15亿元,是国家高新技术企业,拥有高中低端全系列产品,产品覆盖通信、网络安全、工业控制、视频监控、汽车电子、消费电子、数据中心等应用领域。紫光同创立足中国大陆,总部设在深圳,拥有上海、北京、成都等分公司,公司人数超过450人、研发人员占比超过85%,拥有专利近200项、核心专利占比超过85%。

Titan系列是中国第一款国产自主产权千万门级高性能FPGA产品,采用40nm CMOS工艺和自主产权的体系结构,广泛适用于通信网络、信息安全、数据中心、工业控制等领域。·40nm工艺;自主的LUT5架构;创新的软硬件一体化开发流程·系统最高频率500MHz,块存储器资源高达9Mbit·支持多种高速IO接口:SERDES速率5.0Gbps;Logos系列FPGA采用40nm CMOS工艺和全新LUT5结构,集成RAM、DSP、ADC、Serdes、DDR3等丰富的片上资源和IO接口,具备低功耗、低成本和丰富的功能,为客户提供高性价比的解决方案,广泛应用于工业控制、通信、消费类等领域,是客户大批量、成本敏感型项目的理想选择。·灵活可编程的CLM,每个CLM包含4个LUT5和6个寄存器Compact系列CPLD产品,采用55nm eFlash工艺和自主产权体系结构,满足低功耗、低成本、小尺寸的设计要求,适用于系统配置、接口扩展和桥接、板级电源管理、上电时序管理、传感器融合等应用需求,广泛应用于通信、消费电子、无人机、工业控制等领域。·1K~10K LUT4逻辑单元,支持3.3/2.5V内核、或1.2V低电压内核·支持MIPI、LVDS、I2C、SPI、OSC、RAM、PLL等

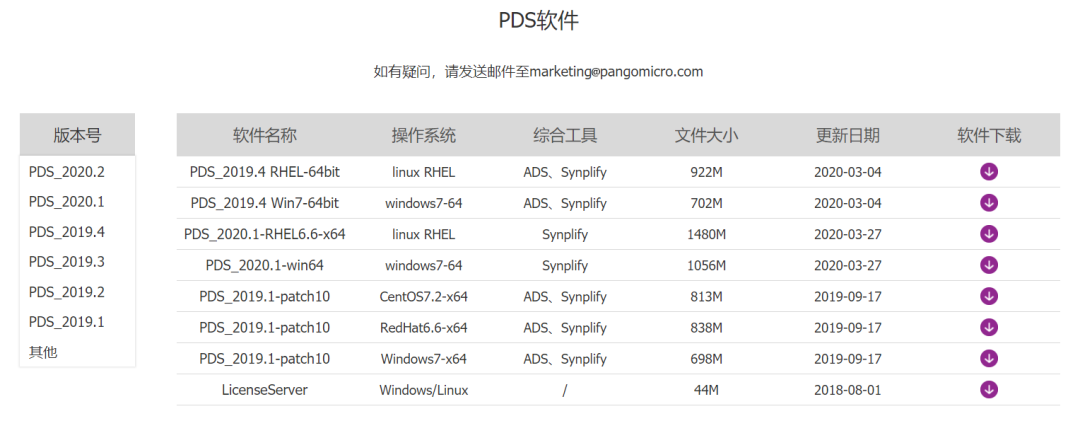

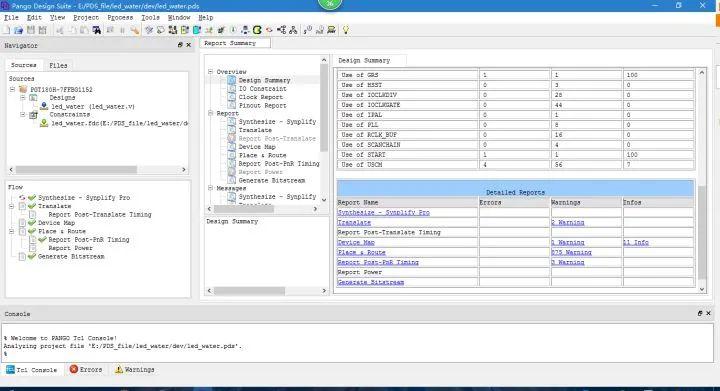

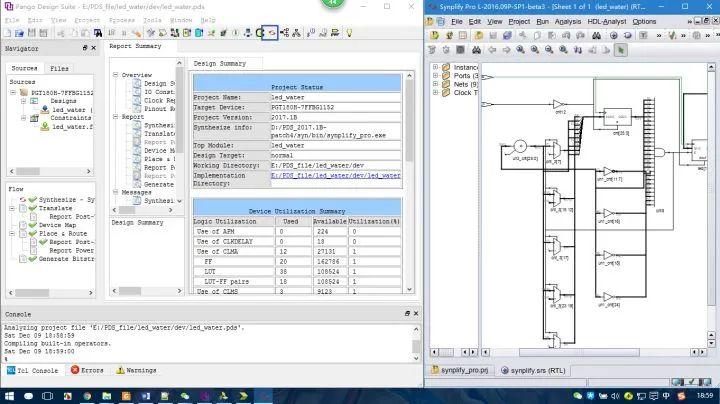

Pango Design Suite是紫光同创基于多年FPGA开发软件技术攻关与工程实践经验而研发的一款拥有国产自主知识产权的大规模FPGA开发软件,可以支持千万门级FPGA器件的设计开发。该软件支持工业界标准的开发流程,可实现从RTL综合到配置数据流生成下载的全套操作。

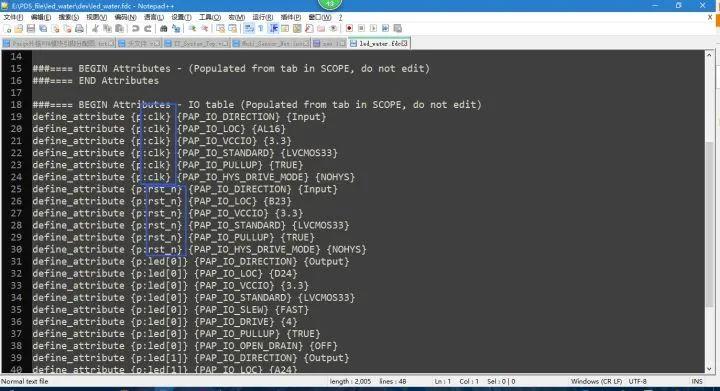

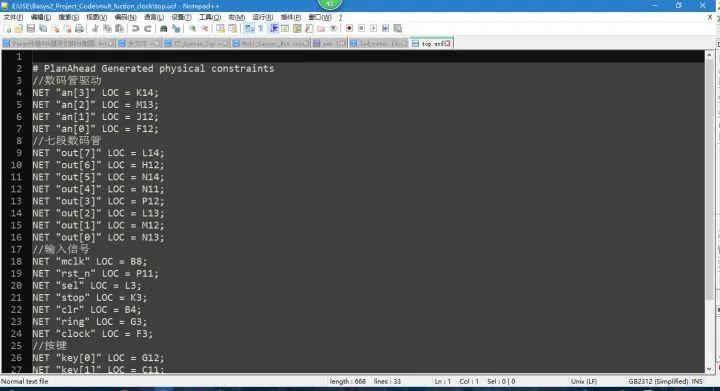

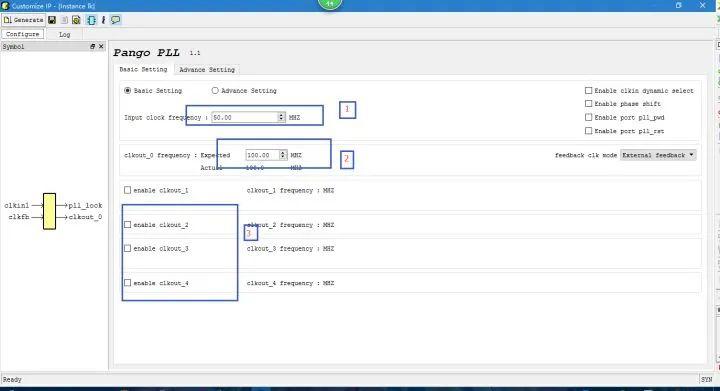

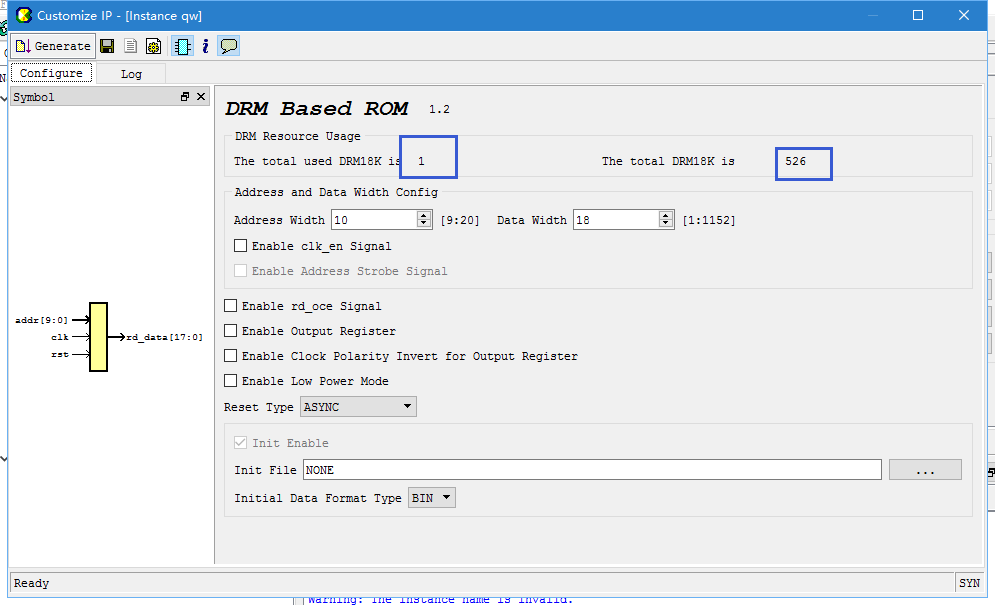

官方可以下载相关的软件和申请license,这一点比较友好。恩,相信已经有朋友看出来了,PDS这个界面还真和ISE有点神似,不过相似没关系,看着还算简洁,而且PDS的软件安装包只有三百多兆,比起其他几款都小了很多,可能是紫光的产品还比较少吧,据我所知,目前紫光只有两款FPGA,X家和A家多的都数不过来了。PDS在编译速度上还是比较慢的,我用我的i3低功耗笔记本实测几款主流综合工具,对于一个流水灯来说。ISE14.7和QuartusII13.0可能不到一分钟就编译完成,Vivado可能是由于内部算法的不同,会有2-3分钟的时间,PDS我没有掐表,目测五分钟是有了。不过对于工程量大的设计,PDS的速度也没有很明显的降下来,我们比赛做的项目最后的大工程,我电脑用ISE14.7跑了有二十分钟吧,PDS用的时间少了一点。综合来说PDS在编译速度上基本与ISE14.7持平,小工程ISE14.7完胜,大工程PDS略占便宜。毕竟ISE已经停更了么。当然在人性化设计和美观上评价,我认为ISE还是好,也可能是我用习惯了吧。对于软件还有很多地方需要说说,比如我们要看自己写的代码的原理图的话,ISE上直接点击Synthesize-XST下的View RTL Schematic便可直接打开,那么PDS呢,需要重新打开一个新的界面(貌似是一个软件),然后才能查看。引脚分配文件的话,PDS后缀为fdc,打开文件里面是这样的。但是紫光的IP使用的话,我是必须要吐槽一下了,首先来说说PLL IP Core的调用,我对于X家和A家的软件的话,我使用的时候感觉很便捷,填写输入时钟,直接填写输出时钟,然后直接输出,至于相位偏移和占空比也是可以直接调的。PDS来了。上图中的1部分是输入时钟的,2部分是输出时钟的,那么下面第3部分就是用2部分倍频的时钟再分频出来,输出你要的时钟,也就是说,比如你需要75Mhz,那么保证是整数分频的话,你需要首先最少需要倍频到150Mhz然后对150Mhz的时钟进行3分频,最后才是输出你需要的时钟,那如果我需要一个99Mhz的时钟呢,对不起支持不了,当然我们实际使用的过程中也不需要那么奇葩的时钟了。接下来时RAM IP Core了,PGT180H的资源很多,芯片里面的存储是一块一块的,一块是18kbit,一共有526个,这算是很大的容量了,你需要的多的时候,它会自动拼接。最多只能用这么多了,再多的话生成两块拼起来也可以,不过一般情况也不会一次用这么多,除非一样显示很大的图片,对,我显示了。最后就是PDS自带的编辑器了,说实话很不好用,虽然ISE也一样很不好用,但是至少软件支持和第三方编辑器级联,但是PDS不支持,所以我这也有一点小建议了,就是希望PDS后面的版本可以支持第三方编辑器级联,记住这是我建议的,后面如果紫光真的支持了,那肯定是听了我的建议。至于软件其他的一些功能使用,我使用时间也不长,就暂且不谈。

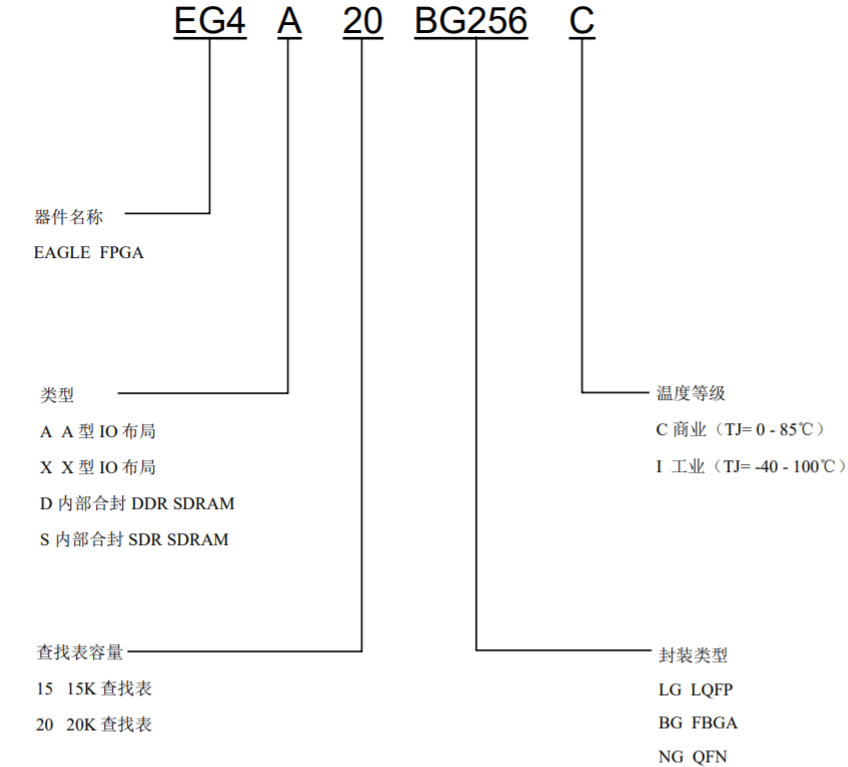

上海安路信息科技有限公司成立于2011年,总部位于浦东新区张江高科技园区。安路科技专注于为客户提供高性价比的可编程逻辑器件(FPGA)、可编程系统级芯片、定制化嵌入式eFPGA IP、及相关软件设计工具和创新系统解决方案。公司创始团队由具有国内外集成电路产业界丰富经验的高级管理人才、工程技术人才和学术界资深科研人员组成。公司研发人员70%以上具有硕士或博士学位,毕业于复旦、交大、清华、北大、中科院、UCLA、UIUC、UCSD等国内外高校。2014年获得中信资本投资 / 2015年获得杭州士兰微集团和深圳创维集团联合投资 / 2017年获得中国电子信息产业集团华大半导体有限公司和上海科技创业投资有限公司战略投资。/2019年获得深圳市创新投资集团有限公司、苏州厚载成长投资管理合伙企业(有限合伙)等战略投资。安路科技量产和在研产品分为三个系列:高端PHOENIX(凤凰)、中端EAGLE(猎鹰)、低端ELF(精灵)。产品在核心架构、软件算法和系统集成等方面拥有多项技术专利。自主开发的全流程TD软件系统和硬件芯片完美地结合在一起,提供了用户从前端综合到位流生成的完全开发平台。目标市场为通讯设备、工业控制、视频监控、人工智能、数据中心等应用领域。

安路科技根植中国,面向世界,积极参与国际竞争,努力成为中国可编程逻辑器件产业的主导企业和世界可编程逻辑器件解决方案的主要供应商。

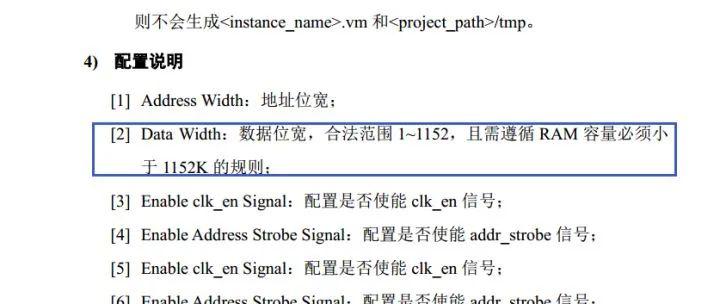

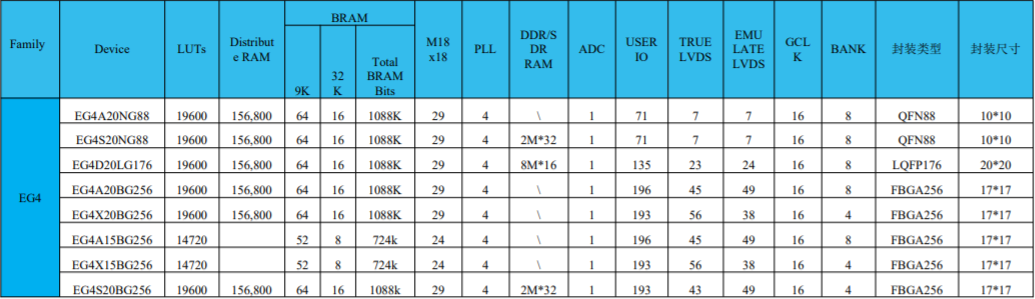

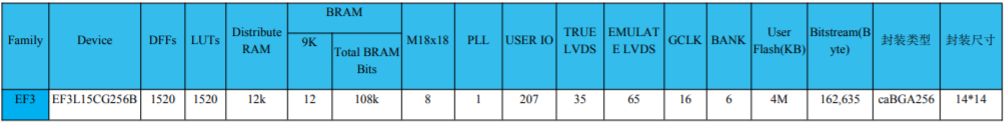

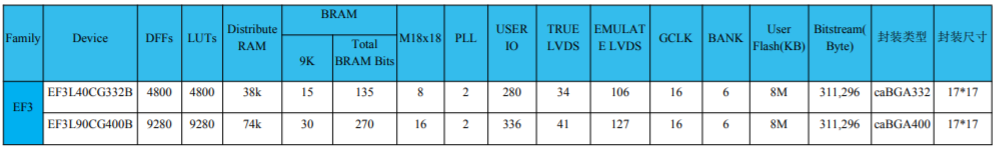

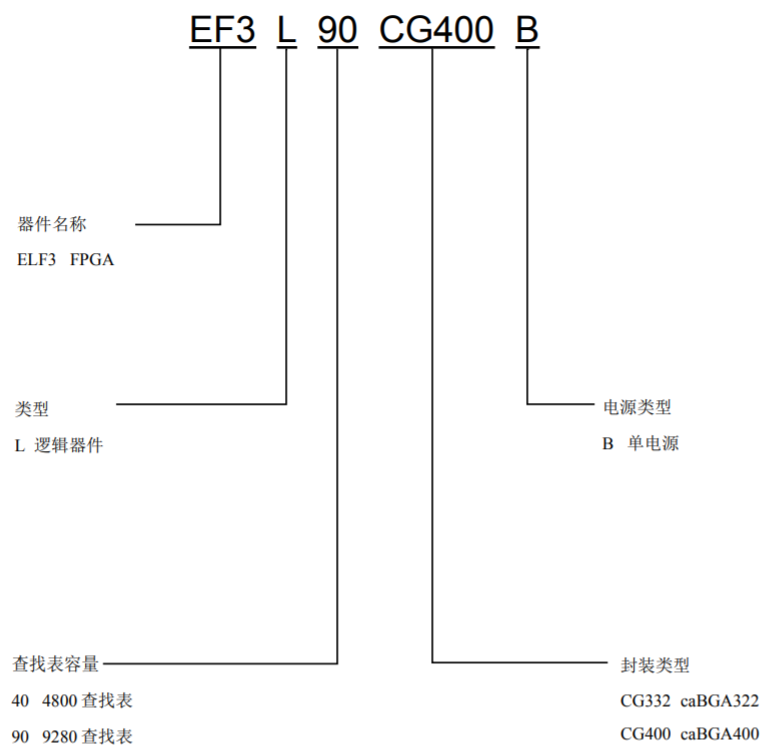

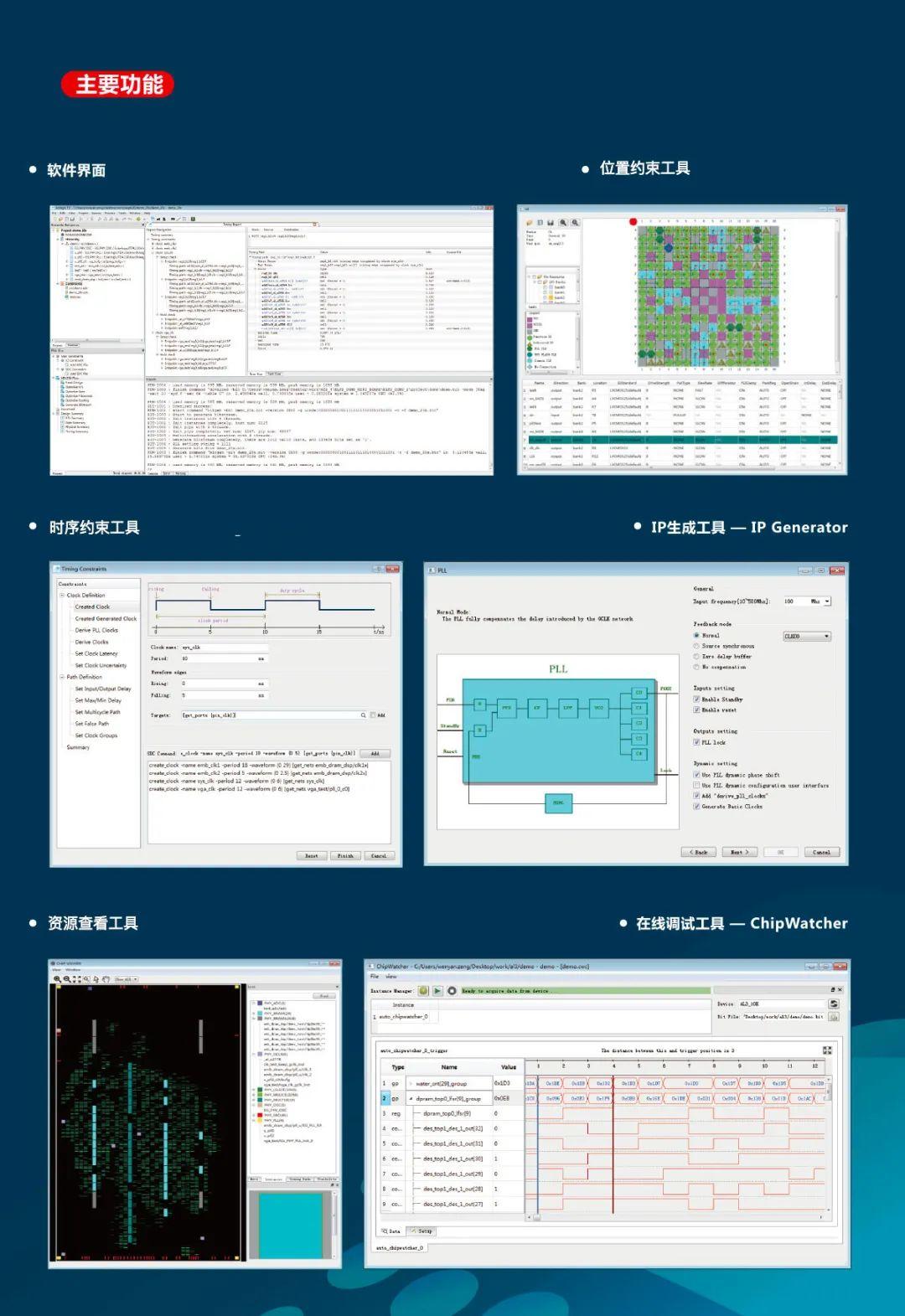

EAGLE 器件系列建立在一个优化的低功耗工艺基础之上,并通过最低的成本实现较高的性能。适当的逻辑和乘法器,丰富多样的片内存储器,高达 1Gbps 的 IO 速率,使得 EAGLE 器件非常适合于图像预处理,伺服控制和高速图像接口转换等领域。 共有 8 种器件,逻辑规模从 14720 到 19600 LUTs,用户 IO 数量从 71 到 196 个 最大支持 156,800 Kbits 分布存储器 嵌入块存储器容量 9 Kbits,可配置为真双口,8Kx1 到 512x18 模式 嵌入块存储器容量 32 Kbits,可配置为真双口,可设置为 2K*16 或 4K*8 部分封装内置 2MX32b SDR SDRAM 存储器 部分封装内置 8MX16b DDR SDRAM 存储器 可配置逻辑模块(PLBs) 优化的 LUT4/LUT5 组合设计 单一 Slice 支持 2 个 M18x18 或 4 个 M9x9 LVCMOS (3.3/2.5/1.8V/1.5/1.2V) PCI SSTL 3.3V (Class I and II) SSTL 1.8V and 1.5V (Class I and II) HSTL 1.8V and 1.5V (Class I and II) 通过配置支持以下差分标准 LVDS,Bus-LVDS, MLVDS, RSDS, LVPECL 针对高速 I/O 接口设计的 2 路 IOCLK 主模式串行 SPI (MSPI) 从模式串行 (SS) 主模式并行 x8 (MP) 从模式并行 x8 (SP) JTAG 模式 (IEEE-1532)安路 EF3L15 FPGA,定位低成本、低功耗可编程市场。无需外部配置器件、低密度逻辑容量、丰富的存储器、高达 1Gbps 的 IO 速率等特性,使得 EF3 FPGA 非常适用于高速接口扩展与转换,高速总线扩展,高速存储器控制等应用场景。 1,520 LUTs 最大用户 IO 数量达 207 个 内置嵌入式存储模块(9K),多种组合模式,可配置为真双口 可配置逻辑模块(PLBs) 优化的 LUT4/LUT5 组合设计 输入/输出单元包含 DDR 寄存器支持 DDRx1、DDRx2 模式 LVTTL,LVCMOS(3.3/2.5/1.8V/1.5/1.2V) PCI 通过配置支持以下差分标准 LVDS,Bus-LVDS,MLVDS,RSDS, LVPECL 针对高速 I/O 接口设计的 2 路 IOCLK 主模式串行 SPI (MSPI) 从模式串行 (SS) 从模式并行 x8 (SP) 主模式并行 x8 (MP) JTAG 模式 (IEEE-1532)EF3 器件是安路科技的第三代 FPGA 产品,定位通信、工业控制和服务器市场,最多支持 336 个 I/O,满足客户板级 IO 扩展应用需求。EF3 器件采用先进的 55nm 低功耗工艺,优化功耗与性能,并可以通过低成本实现较高的功能。器件旨在用于大批量、成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。 共 2 种器件,规模从 4800 到 9280 LUTs 最大用户 IO 数量达 336 个 内置嵌入式存储模块,多种组合模式,可配置为真双口 可配置逻辑模块(PLBs) 优化的 LUT4/LUT5 组合设计 输入/输出单元包含 DDR 寄存器支持 DDRx1、DDRx2 模式 LVTTL,LVCMOS(3.3/2.5/1.8V/1.5/1.2V) PCI 可配置支持以下差分标准 LVD,Bus-LVDS,MLVDS,RSDS,LVPECL BANK 0 和 2 支持 True LVDS 输出,所有 BANK 均支持单端和差分输入 LVDS 接口高达 1Gbps 支持热插拔 针对高速 I/O 接口设计的 2 路 IOCLK 从模式串行 (SS) 从模式并行 x8 (SP) 主模式并行 x8 (MP) JTAG 模式 (IEEE-1532)Tang Dynasty (TD) 软件是安路科技自主开发的从HDL描述到最终位流下载和片上调试的完整系统,为安路科技所有FPGA芯片产品系列提供简洁可靠的应用设计开发环境。TD软件系统采用基于统一数据库的层次化设计,核心优化引擎采用创新的设计自动化技术,主体流程是性能驱动的逐步精确迭代优化进程。TD软件系统支持工业界标准的设计输入描述,提供良好的第三方设计验证工具接口。官网有软件可以直接下载,因为使用人数较少,网上很少能找到使用教程。·创新的软件算法有效支持ELF、EAGLE、PHOENIX等系列各个规模的器件·可扩充的软件架构快速支持包括单芯片、SIP、IP核在内的多品种产品系列·结构化的软件开发平台支持对硬件新结构的快速准确模拟和评估

京微齐力(北京)科技有限公司注册在北京经济技术开发区,总部设于亦庄,在中关村设有研发中心;在上海,深圳有技术支持,市场销售团队。京微齐力是除美国外最早进入自主研发、规模生产、批量销售通用FPGA芯片及新一代异构可编程计算芯片的企业之一。公司团队申请了近200件专利和专有技术(含近50件PCT/美国专利),具备独立完整的自主知识产权。其产品将FPGA与CPU、MCU、Memory、ASIC、AI等多种异构单元集成在同一芯片上,实现了可编程、自重构、易扩展、广适用、多集成、高可靠、强算力、长周期等特点。产品所服务的市场将迅速超过几百亿,而随之衍生的终端模组、应用方案的市场规模将达数千亿。得益于混合架构,这类芯片硬件结构可通过软件来定义,产品能跟随市场的需求发展而相应变化。相比传统专用芯片平均2年的生命周期,应用于多个产业链的新型异构可编程计算芯片的生命周期可长达10年。公司技术与产品将涵盖可编程FPGA内核,异构计算与存储架构、芯片设计、软件开发、系统IP应用等相关技术领域。公司提供核心关键芯片和相关市场应用系统解决方案。

基于先进的创新可编程技术,研发新一代面向人工智能/智能制造等应用领域的AiPGA芯片(AI in FPGA)、异构计算HPA芯片(Heterogeneous Programmable Accelerator)、嵌入式可编程eFPGA IP核(embedded FPGA)三大系列产品,产品市场将涵盖云端服务器、消费类智能终端以及国家通信/工业/医疗等核心基础设施。

| | |

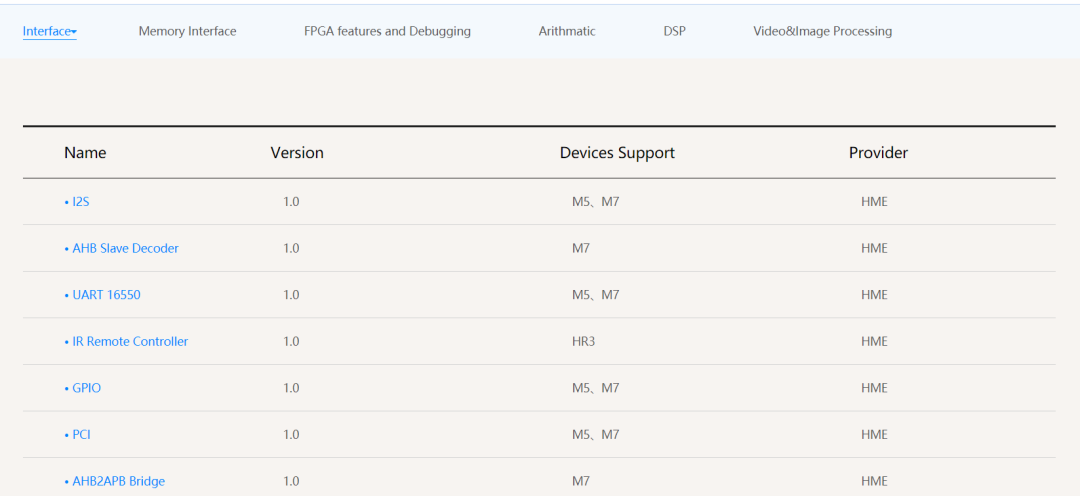

| | 详见官网介绍:http://www.hercules-micro.com/product/index86.html |

| |

| |

| |

| |

| |

FX是自主研发的一款EDA设计工具,您可以使用它快速、高效地进行FPGA和SoC应用设计。用户通过使用FX完整的EDA工具链与丰富的IP资源,可以有效的进行快速应用研发,缩短产品开发周期。同时FX友好的交互式集成开发环境可以支持多种广泛使用的第三方设计工具进行协同设计,从而进一步加速用户的设计与验证过程。·与第三方工具无缝连接 (Prime Time和ModelSim等)FX是自主研发的一款EDA设计工具,您可以使用它快速、高效地进行FPGA和SoC应用设计。用户通过使用FX完整的EDA工具链与丰富的IP资源,可以有效的进行快速应用研发,缩短产品开发周期。同时FX友好的交互式集成开发环境可以支持多种广泛使用的第三方设计工具进行协同设计,从而进一步加速用户的设计与验证过程。上海复旦微电子集团股份有限公司是从事超大规模集成电路的设计、开发和提供系统解决方案的专业公司。因为复旦微电子FPGA只对军工、研究院所供货,所以这方面信息不方便透漏太多,网上也基本上无此相关信息和使用教程,这里也不多说了,如果你是这两方面应用应该很好联系到官方,相关的信息也会获得,如果不是拿到信息也没有什么用,因为你买不到芯片。

K7、V7 325、690系列都有,大容量彰显实力,并兼有抗辐射产品、ZYNQ产品(复旦微电子的FMQL系列,该FMQL系列中两款芯片中FMQL10S400对标的Xilinx的7010,FMQL45T900对标的是Xilinx的7045。)

可惜或只军工可用,虽对外售卖,但得是军品、研究院所项目。

毫无疑问,中国FPGA产业与同行的领先厂商相比是有差距的:

按照京微齐力王海力的说法,从芯片角度看,国内的FPGA与国际厂商有两代半的工艺线。现在国际厂商已经在16nm产品上量产了,而国内厂商目前只做到40nm,28nm产品还在推进阶段,他强调。

如果从软件和生态方面看,国内FPGA企业与国际领先厂商之间更是有八到十年的差距。如果想追上,尤其是在中高密度产品上追上国际领先者,国内FPGA厂商还需要很长的一段路要走。

高云半导体工程副总裁王添平先生也表示,目前活跃在市场的国产FPGA产品中,多以中低密度产品为主。这些产品从定义、芯片设计、生产工艺、芯片封装、应用软件、乃至实际销售,都有不错的表现,高云的低密度产品在某些细分领域正在全面取代国外厂商。但在他看来,对于国内大部分的中高低密度的FPGA,其架构都逃不开LUT+布线的概念,具体到产品,各自侧重的技术、IP乃至相应的应用市场也都是各有针对性。如果从这个角度看来,国产厂商在中高密度FPGA的技术水平与国际领先厂商相比,在硬件设计和软件方面还有一定的差距。

虽然差距很明显,但对于国内厂商来说,负重前行是一种必然的使命。尽管FPGA全球市场销售额近年来的年增长率一直徘徊在个位数,但其进入各类新兴市场如大数据、人工智能、云计算、硬件加速、汽车自动驾驶以及消费等领域的速度却非常吸引眼球,乃至人们对FPGA特别是国产FPGA的未来发展充满期待,资本进入该领域也日趋活跃。

说明:本文来源网络;文中观点仅供分享交流,不代表本***立场,转载请注明出处,如涉及版权等问题,请您告知,我们将及时处理。