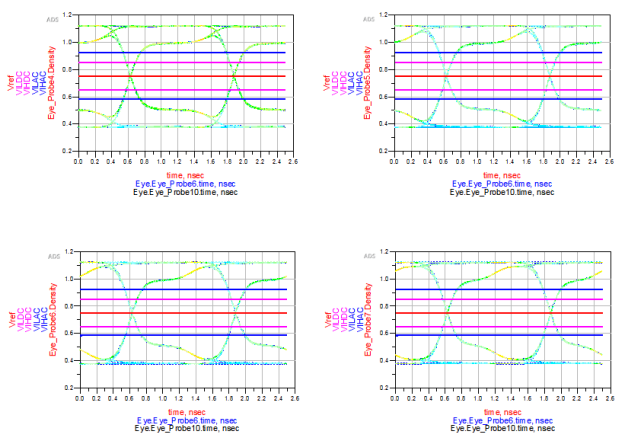

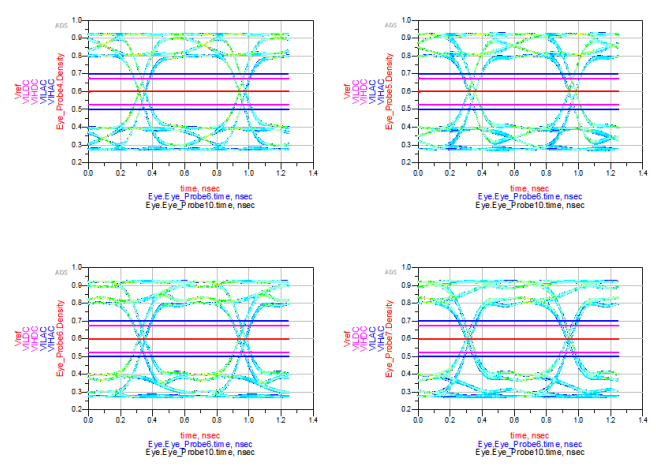

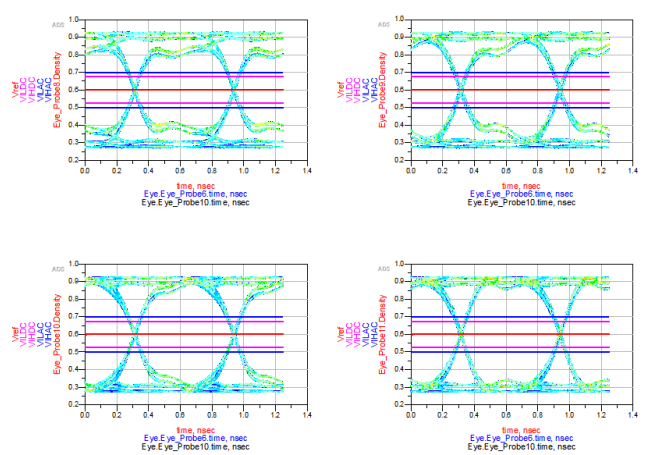

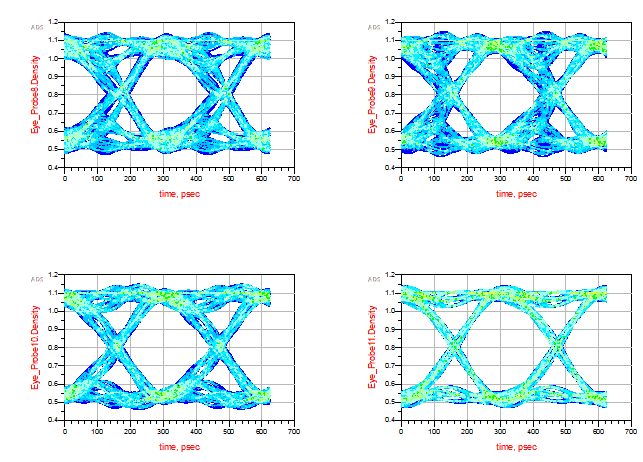

信号完整性仿真:DDR3/4/5系列地址信号端接优化对比

二、我的精品课

《DDR3/4/5系列信号完整性仿真24讲》为信号完整性课程的DDR系列,系统的讲述了DDR3、DDR4协议对比,信号质量关注点,并对各个信号进行了仿真评估,从时域软件仿真到提取S参数后再仿真波形,对各类信号的影响参数进行了透彻的探究;

同时,视频还对几个不同软件仿真出来的波形进行了对比;最后,在视频的最后,还对DDR5进行了一些展望,对高达6400bps的DQ信号和与之对应的ADD信号进行了仿真。以下是课程安排

从根本上明白DDR信号仿真的关注点; 对DDR3、DDR4的协议提炼、对比;

学会使用speed2000按照DDR信号分组仿真DDR信号质量和时序;

学会使用PowerSI软件提取DDR信号S参数;

学会处理地址信号端接电阻;

学会ADS、hyperlnx扫描DDR信号质量,并对比不同软件的信号波形;

展望DDR5,仿真DDR5的地址信号、DQ信号;

学会设计仿真;获得课程有关的模型和相关学习资料。

高校在校生;

信号完整性仿真人员;

信号完整性测试人员;

硬件开发人员;

PCB layout人员。

3、读者福利(扫码立即领取)

以上资料在本文附件直接下载,如果遇到麻烦(因下载量大,百度云盘可能会失效)请在文章下方留言或者直接联系平台客服一对一领取。

作者:开仿啦 仿真秀专栏作者

登录后免费查看全文

附件

著作权归作者所有,欢迎分享,未经许可,不得转载

首次发布时间:2022-12-01

最近编辑:1年前

作者推荐

还没有评论

相关推荐

最新文章

热门文章