DDR3/4/5系列信号完整性仿真50讲:掌握DDR协议和仿真关键技术要点-含Sigrity仿真全套

服务:

- 课程资料下载

- 90天知识圈

- 在线开票

- 提供培训通知

- 交流群

本课适合哪些人学习:

1、高校在校生;

2、信号完整性仿真人员;

3、信号完整性测试人员;

4、硬件开发人员;

5、PCB layout人员。

你会得到什么:

1、从根本上明白DDR信号仿真的关注点;

2、对DDR3、DDR4的协议提炼、对比;

3、学会使用speed2000按照DDR信号分组仿真DDR信号质量和时序;

4、学会使用PowerSI软件提取DDR信号S参数;

5、学会处理地址信号端接电阻;

6、学会ADS、hyperlnx扫描DDR信号质量,并对比不同软件的信号波形;

7、展望DDR5,仿真DDR5的地址信号、DQ信号;

8、学会设计仿真;

9、获得课程有关的模型和相关学习资料。

课程介绍:

一、关于课程

本课程为信号完整性课程的DDR系列,系统的讲述了DDR3、DDR4协议对比,信号质量关注点,并对各个信号进行了仿真评估,从时域软件仿真到提取S参数后再仿真波形,对各类信号的影响参数进行了透彻的探究;

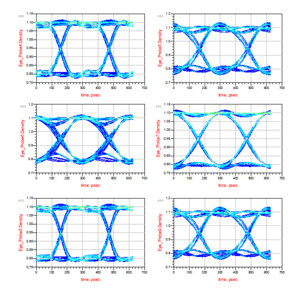

同时,视频还对几个不同软件仿真出来的波形进行了对比;

最后,在视频的最后,还对DDR5进行了一些展望,对高达6400bps的DQ信号和与之对应的ADD信号进行了仿真;

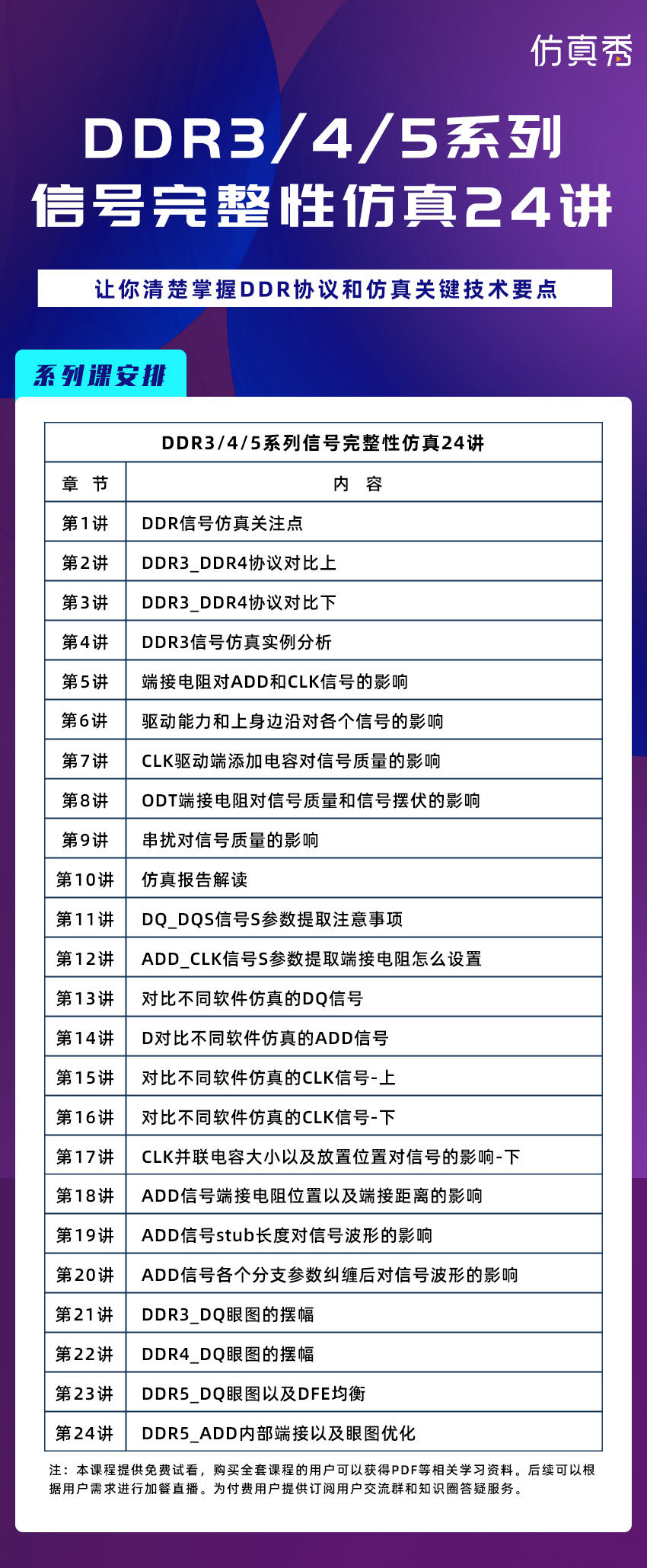

二、课程安排

课程目录

第1讲 DDR信号仿真关注点

第2讲 DDR3_DDR4协议对比上

第3讲 DDR3_DDR4协议对比下

第4讲 DDR3信号仿真实例分析

第5讲 端接电阻对ADD和CLK信号的影响

第6讲 驱动能力和上身边沿对各个信号的影响

第7讲 CLK驱动端添加电容对信号质量的影响

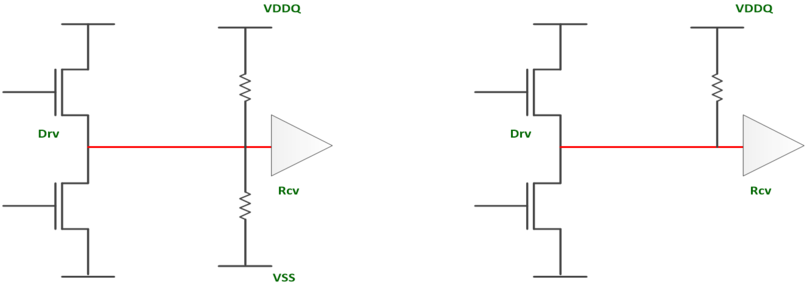

第8讲 ODT端接电阻对信号质量和信号摆伏的影响

第9讲 串扰对信号质量的影响

第10讲 仿真报告解读

第11讲 DQ_DQS信号S参数提取注意事项

第12讲 ADD_CLK信号S参数提取端接电阻怎么设置

第13讲 对比不同软件仿真的DQ信号

第14讲 D对比不同软件仿真的ADD信号

第15讲 对比不同软件仿真的CLK信号-上

第16讲 对比不同软件仿真的CLK信号-下

第17讲 CLK并联电容大小以及放置位置对信号的影响-下

第18讲 ADD信号端接电阻位置以及端接距离的影响

第19讲 ADD信号stub长度对信号波形的影响

第20讲 ADD信号各个分支参数纠缠后对信号波形的影响

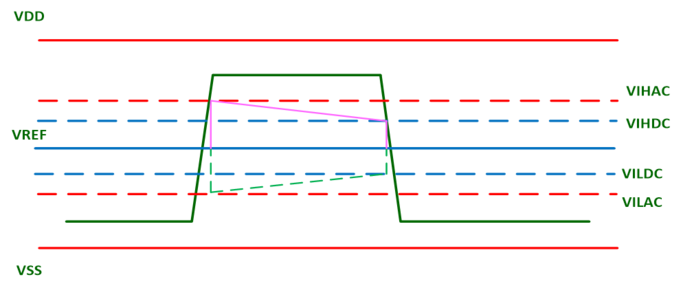

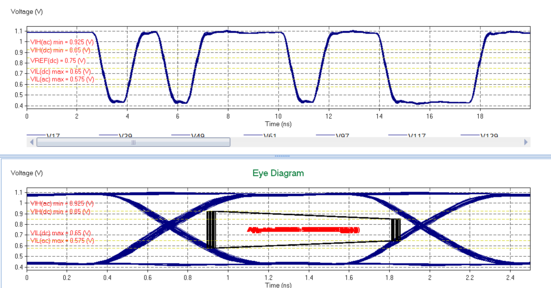

第21讲 DDR3_DQ眼图的摆幅

第22讲 DDR4_DQ眼图的摆幅

第23讲 DDR5_DQ眼图以及DFE均衡

第24讲 DDR5_ADD内部端接以及眼图优化

三、讲师介绍

开仿啦,SI、PI从业者,对SI、PI问题有深入研究,坚持理论基础为底蕴,个人能力为核心,软件为手足的工作理念,着重培养知识底蕴和能力底蕴。

四、其他

1、IOS系统用户请不要在苹果商店充值秀币购买,以免给用户带来不必要的麻烦,建议用户在仿真秀官网通过微 信或支付宝购买后,支持在苹果电脑和手机上观看。

相关内容推荐

课程相关图片: