电源分配网络(PDN)基础知识

说到电源完整性,先不说电源复杂的互连系统,单电源分配网络(PDN)部分在产品设计中就需要足够关注。

电源分配网络包含从源端稳压模块(VRM)到芯片,芯片分配电压,再到电源路径(单层直达或过孔转换的几个层面),最终流向使用芯片或终端设备。

电源路径与信号路径是有区别的,电源分配网络中一个电源路径可以在一个节点分成多个路径,或者说转换成多个电源,终端挂多个元器件,可以理解为一对多。而信号路径只能一对一。

既然电源分配网络是为终端设备提供所需电源,那就是有要求,就需要对电源分配网络管控。路径上电压是有变化的,那么电源分配网络的电流就会有波动,在这种情况下,就需要保持电源分配网络阻抗低于目标阻抗。

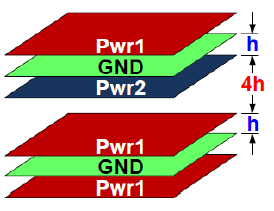

目标阻抗的管控说到底就是路径管控。两个因素:电源和地平面之间介质尽量薄,尽量短而宽的走线。

下图为消费类产品设计电源部分的实际情况图:

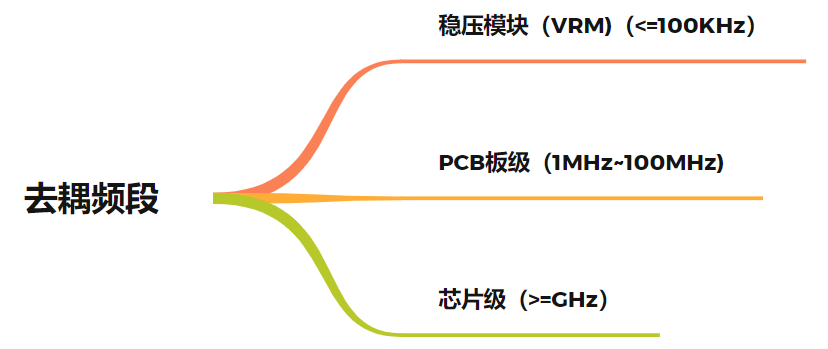

板级电源分配网络设计的频率范围约从 1MHz 到 100 MHz。这正是电路板平面和多层陶瓷贴片电容器( MLCC) 发挥作用的频率范围 。这也是仿真时,重点关注的频率范围。

简单来说,低频率段由稳压模块来平衡,高频率段由芯片片选电容来解决,中间的频段就是板级来管控。

我们说的PDN设计一般就是指在PCB板级上给电源提供低阻抗路径。这里面还有电容摆放位置、电容不同容值&个数、反谐振等方面,到仿真这一边,就是交流部分:PDN阻抗提取和直流部分:IR Drop压降。

当交流电流通过电源路径时,电源分配网络上也将产生电压降,这个压降会随着频率发生变化。电源路径的不同(层数&Shape宽度等),造成的压降变化是不同的,输出稳定电压到终端的难度很大,我们所要做的只是保证电压的变化在一定的范围之内,也就是所谓的噪声容差。上式就可能转换为目标阻抗:

PCB板级PDN设计,需要先确定板级电源分配网络的设计目标阻抗。举例:1.2V的CPU用电为例,纹波百分比5%,最大电流为1.2A,根据公式:

上图说明,是否使能电容对PDN阻抗的影响很大。

三个软件的操作上来看,Sigrity&SIwave操作方式比较简单,和寄生参数的提取大体相当。

Sigrity电容模型

只是容值模型部分需要关注与研究,特别针对实际产品设计和优化。

或许是不常用也或许是其他原因,ADS上操作相对比较麻烦,花费的时间也比较长,这个时间是指EM仿真时间(30分钟以上)。不知道ADS新的版本或者操作上有没有更新改善。

反正这一通下来,感觉就是:一顿操作猛如虎,看到结果心里苦。最终,放弃了。

看到S参数就知道有问题。感觉应该是在叠层设置或者端口的设置那边出了问题。

叠层的部分,负片层方向;

端口的部分,Port负端方向。

三个软件操作步骤:

PDN提取的的时候,ADS软件给出频率扫描范围的建议,最高500MHz。

仿真出的结果对比:

end