实例分析ESD电磁兼容问题

本文摘要:(由ai生成)

本文通过实例分析了电子产品在设计中如何防范ESD伤害。智能手表因ESD损坏电容导致反复开关机,通过替换电容和增加GND露铜解决;USB接口外壳ESD干扰敏感信号致黑屏,通过固定PIN并远离敏感信号解决;屏幕朝下时ESD导致黑屏,修改SPI协议解决;USB GND PIN注入ESD致概率性关机,增大电容容值、改进FPC走线解决;屏幕朝下ESD接触放电致TP失效,确保TP接地解决。这些案例为电子产品设计提供了ESD防护的实用策略。

ESD对于很多电子产品是一个致命硬伤,如何设计好产品的ESD,是需要花很多时间和精力来研究的。下面通过几个实例来和大家一起分享下。

根据反复重启的时间判断,类似于长按Power键。检查Power_On信号,发现已经被持续拉低,Power_On信号的原理图如下:

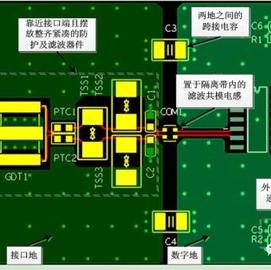

为了降成本,位置1并没有贴TVS管,而是用一个电容代替,电容的耐压值是25V。失效的机器,这个电容已经短路,可以判断ESD进入壳体,直接打坏了位置1的电容。如果把位置1的电容耐压提高到50V,能抗的ESD枪数量会增多,但最终还是会坏。这个项目不是防水的,密封性做得很差,所以才有问题。把位置1的电容换成TVS管,或者位置1不要贴任何东西,在位置2放一个1nF的电容。靠1K电阻+1nF电容来吸收ESD能量。另外,在侧键的FPC附近,增加了GND露铜区域,引导ESD先进入GND。这也是一种低成本的解决方法,如果ESD能量足够大,实测几乎可以把1K电阻打坏。某智能手表在USB接口外壳打ESD造成黑屏死机问题 充电口是Micro-B型USB接口,接触放电±10KV,会出现黑屏,死机,闪屏等现象。将USB信号逐个引出,VBUS,D+,D-都没有出现问题,打ID管脚,会出现类似现象。打GND,会很低概率出现类似现象。遂将问题定位到ID管脚,和GND上。1、USB_ID管脚是悬空的。

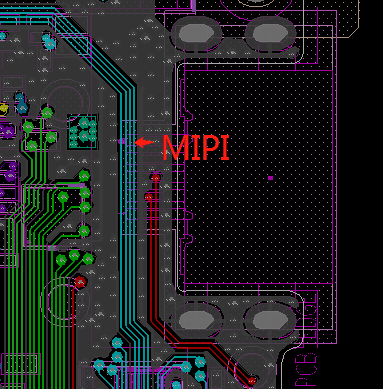

2、在L3和L6层,靠近USB接口,有与屏相关的敏感信号。

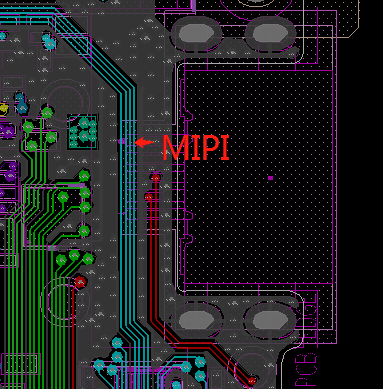

悬空的ID管脚是知名威胁,静电积累到一定程度,肯定会对周围放电,二次放电的威力更大。USB周围的有敏感信号,在打ESD时,附近的GND电平瞬间局部抬高,尤其是看到USB接口的屏蔽壳跟表层相连,周围没有非常多的过孔打到内层GND,这更加重了GND局部电平的提高,这会干扰到这些敏感信号,导致死机,黑屏,闪屏问题。USB的固定PIN以及GND PIN,只接主GND,不要每一层都接GND。MIPI,LCD_TE,LCD_RST远离USB接口。这是一个SPI接口的显示屏,问题比较简单,一个偶然的机会发现是SPI信号中,CS线被软件强制拉低,且一直处于低的状态,这样是不行的。

实测将CS线的行为改成符合SPI协议,只在传输数据时拉低,这个黑屏的问题解决了。某智能手表在USB的GND PIN上注入接触-8KV静电,会概率关机 直接拆开整机,在主板的不同地方的GND,注入ESD,统计关机的次数,得出一个简单的规律,只有在靠近电池BTB的地方,才会大概率出现,初步判断是ESD干扰了电池周围的信号。电池BTB周围的信号有D+,D-,VBUS,MIPI,BAT_ID,BAT_THERM等,逐个在这些信号上,注入小两级的ESD,比如±2KV,有些信号会导致PMU损坏,有些会导致死机。只有BAT_ID信号会出现关机的现象。

关机有两种可能,一是内部软件流程关机,二是电池突然掉电。尤其是第二种,往往很容易忽略。因为某些情况下,ESD注入两枪,立即就出现了关机现象,这很像是电池掉电了。

电池掉电有两种可能,一是电池保护板保护机制生效,切断了供电。二是Vbat到PMU的通路被打断。排查了主板上的器件,Vbat的通路经过的都是一些模拟器件,可能性比较小。我们直接从主板VBAT飞线,连接到程控电源上,再打ESD的时候,发现就不会关机了。这进一步说明,在注入ESD时,是电池本身没有输出了。

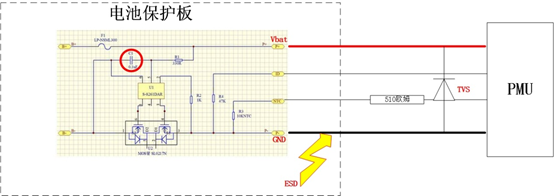

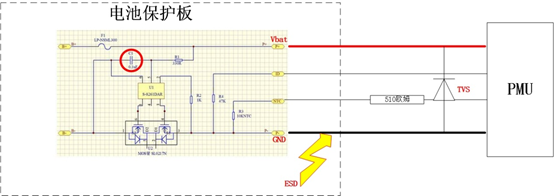

电池保护板的原理图如下:

在图中GND上注入+8KV,没有问题,因为右边的TVS吸收了大部分能量,由于正向导通,钳位电压较低(小于4.4V),电池保护板没有触发保护机制。但是如果注入-8KV,TVS管开始反向钳位,瞬间的钳位电压较高(大于4.4V),超过电池起保护电压,电池触发保护机制,MOS管U2断开,导致关机。下图是TVS管的钳位特性,也能佐证这个结论。

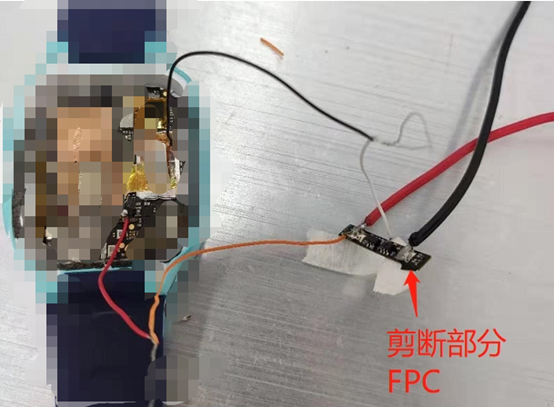

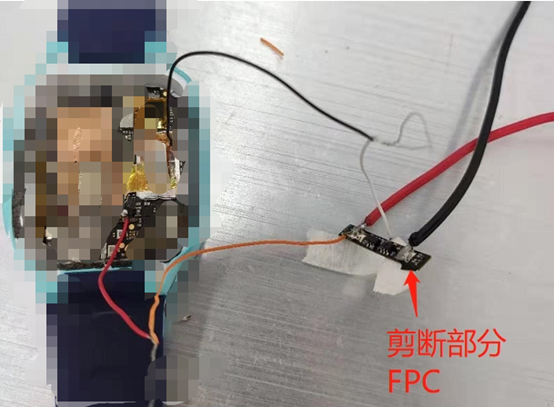

注意电池保护板的保护IC,是判断C1两端的电压,来决定是否起保护的。所以要解决这个问题,需要增大C1的容值。实测将C1增大到1uF,关机的概率明显降低了。降低了,但没有彻底解决问题,肯定还有其他原因。这个原因是先猜出来,然后试验验证的。上文提到只有BAT_ID信号会出现关机的现象。所以猜测静电耦合到了ID管脚,进入PMU导致关机。下面是这次电池保护板的走线,ID的走线与GND有较长的耦合长度,GND上的瞬间能量能很快耦合到这根线上,最终直接进入到PMU。

虽然主板上ID走线也跟GND有很长的耦合距离,但是主板上的GND与Vbat之间有TVS钳位,GND的电压不至于跳变太厉害,也不会耦合很多能量到ID线上。反而是电池FPC上的GND电平跳动最大,ID线在FPC上耦合的能量更多。FPC改版成如下样式,ID和GND基本没有重叠区域,能量也不会耦合到ID管脚上,再也没有出现过关机问题。经检查,确定是TP IC被打坏。没有仔细分析IC损坏的原因,因为发现TP FPC背后的双面导电胶太弱,根本没有粘到GND上。TP没有很好接地,导致了这个问题。

只要TP接地良好,就肯定不会出现TO IC失效问题。