SIMULIA CST 扭转乾坤|PCB与接地层之间耦合的EMC仿真

在本文中,我们展示了基于SIMULIA CST的仿真能如何帮助提高产品的发射性能。我们对印刷电路板(PCB)和参考层中信号走线之间的耦合进行分析,因为其通常是电磁兼容性(EMC)测量中值得关注的结果。我们针对传导发射探讨所展示的结果,不过其可以扩展至辐射发射。

传导发射测试背景

传导发射(CE)测试包含对线路中的电流或线路阻抗稳定网络(LISN)中端口电压的测量。在汽车领域,测试装置由被测设备(EUT)、电线、LISN、电磁干扰(EMI)接收器、CAN等通信设备、负载(若需要)以及接地层组成,接地层代表汽车底盘和电压参考。

图1描述了一个简单的测试装置:Vbat和GND分别代表电源正极性和负极性的导线。在我们的案例中,EUT是一个简单的“印刷电路板”(PCB),不过其可以代表任何其他电气或电子系统。CE测试过程中的EMC性能包括将测得的电压/电流与CISPR25等标准定义的限值进行比较,此标准是汽车领域应用最广泛的标准。在我们的案例中,我们重点关注电压方法。测量的选择并非一种限制,因为依据电压法和电流法的测试是等效的。

图1:用于传导发射测试的EMC测试装置

被测设备(EUT)说明

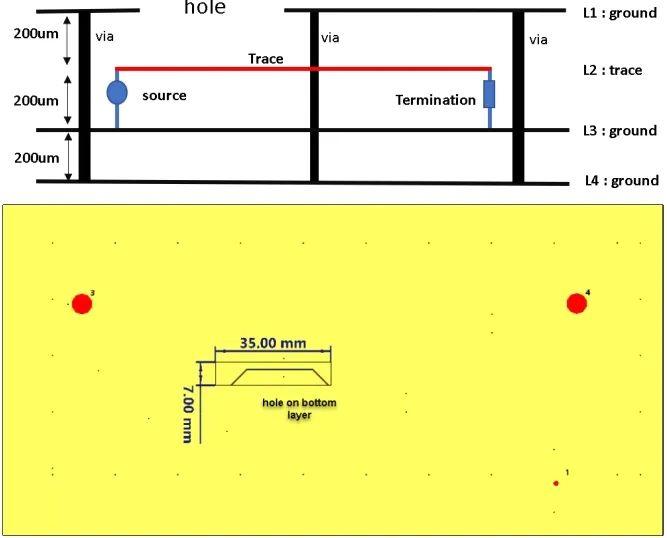

在本研究中,EUT是一个简单的PCB,其包含多个接地层,并且有一条由信号激发的走线。我们利用它来说明走线和接地层之间的耦合,同时解释相关布局如何影响这种耦合。我们研究三个案例:

案例1包含一个2层PCB。激发的走线位于底层。顶层是PCB接地参考层(参见图2)。

案例2包含一个4层PCB,而激励走线位于两个用于传播信号的实心PCB参考层之间(参见图3)。

案例3与案例2相同,不过走线正下方底层有一个小孔(参见图4)。

图2:案例1 PCB插图,PCB底视图

图3:案例2 PCB插图,PCB底视图

图4:案例3 PCB插图,PCB底视图

案例2与案例3被简化为三层而非四层。事实上,L4经过抑制可以简化相关模型,同时降低相关结果的解释难度。因为L3和L4之间不存在噪声源,并且它们之间可能存在的电压可以忽略,所以这种简化并不影响最终结果。此外,接地层也可以成为通过去耦电容器连接的电源层。在我们的案例中,电容器被视为理想器件,并且各层通过多个过孔相互连接,以确保它们之间具有最小阻抗。因此,三层的PCB模型可以代表完整的四层系统。

PCB为矩形,尺寸为21厘米*10厘米,而走线长度为21厘米,线走宽度为0.25毫米,如图5所示。

图5:PCB尺寸与迹线长度

传导发射测试装置

该装置由PCB以及由20厘米长的线路将PCB参考层连到LISN阻抗的连接组成。电源通常通过两条线路连接到PCB:一条用于正极性,另一条用于负极性。在我们的研究中,我们仅用一条接地线来替代这三条电源线。

此次研究中仅考虑共模,因为这是用于耦合的最主要模式。事实上,正负线路之间的输入阻抗可以忽略不计。它们通常通过电容器进行连接,其在此次研究中假定是理想器件。

测试装置的3D模型如图6所示。电路板垂直放置,走线位于底层,而接地线连接到顶层。PCB与接地层之间没有局部接地连接。

图6:测试装置的3D模型

噪声源与终端

走线由来自缓冲器或微控制器的信号激发,并由固定阻抗终止。它对时钟或具有某些高频分量的通信信号进行建模。在仿真过程中,激励是处于100kHz~300MHz频段的宽带电压源。终端是一个50kΩ的电阻。对于所研究的频段,终端阻抗的精确值无关紧要,不过其具有足够高的值,以便使电容耦合占据更加主导的作用。

仿真方法

对于3D仿真,采用全波频域(FD)求解器。其是分析100kHz~200MHz频段内PCB的最佳选择。首先采用FD求解器实现3D模型的构建、网格化和求解。然后,我们采用基于CST Studio Suite原理图的协同仿真、根据3D仿真的结果进行电路仿真。

相关配置是根据连接到我们希望分析的每个端口的阻抗与组件单独进行定义的。也就是说,我们可以在无需重复求解3D模型的情况下修改终端与驱动值并获取LISN电压。这样可以显著缩短仿真时间。另外,在协同仿真设计流程中,我们可以在考虑所有驱动与终端电路的情况下利用“合并结果”功能来计算3D模型中的电流与电磁场。这种可视化功能对于开展研究非常实用。其可以深入分析每个仿真配置的耦合过程。所研究的电路很简单,如图7所示。

图7:“两层”案例1和“三层”案例2的仿真电路

我们注意到,在仿真案例中,GND线路直接连接到PCB,不过其可以通过“共模电感”(CMC)等任何阻抗断开或连接,因为许多设计方案中都是这种情况。

仿真结果

当走线被1V宽带噪声源激励时,我们使用交流分析来分析LINS上的电压。获得的结果如图8所示。在“单层”案例1中,耦合比是78dB,也就是说,对于走线施加1V电压时,我们在20MHz频率得到42dBµV,其超越了CISPR 25传导发射第5类“窄带噪声”的要求。此电平在“双层”案例2中降低到非常低的-58dBµV。在“带孔走线”案例3中,耦合电平是25dBµV,它意味着与案例2相比提高了83dB。事实上,根据CISPR 25第5类的要求,案例3代表传导发射存在高风险。整个结果表明,走线上下方接地层的小孔会削弱我们采用3或4层已经达到的82dB(从-58dBµV到25dBµV)改善的效果,而不采用3D仿真很难做出这个推论。

图8:根据LSIN阻抗计算的案例1、案例2和案例3的电压

耦合机理分析

此时立即出现的第一个问题是:PCB与接地层之间仅仅存在一条连接,LISN中为何会存在电流?我们可以使用20MHz的电场监控器来回答这个问题,请参见图9。我们可以明确地看出PCB与接地层之间存在电场。此电场的变化会通过PCB与接地层之间的杂散电容感应出位移电流,如图10所示。此位移电流会在LISN阻抗中感应出电压。

图9:案例1在20MHz下的场监控器

图10:PCB与接地层之间的电容耦合

当走线如案例2那样敷设在两个接地层之间,则走线与接地层之间的耦合会得到显著降低。事实上,走线与接地层之间的耦合显著提高,而且会改变内层之间的局部电流分布。由于电场被限制在走线与PCB层之间,因此PCB层的外表面不存在电流,而且它们与接地层之间也不存在电场。这减少了PCB与接地层之间的耦合。

图11:降低耦合的插图

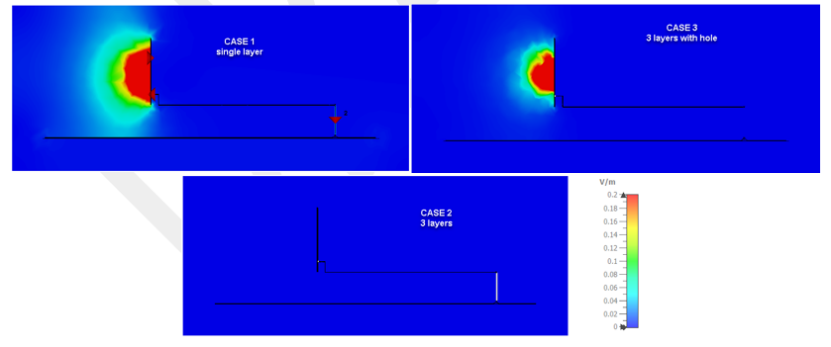

当PCB层如“案例3”那样包含位于走线上方的小孔,则耦合电平接近“单层”案例1的电平,如图12所示。差值只有33dB。显然,该值随着小孔的位置和尺寸发生了变化。

图12:三个案例20MHz时的电场

结论

我们采用3D仿真来研究传导发射测试装置中PCB与接地层之间的耦合。结果表明,由高阻抗端接的走线可以在它与接地层之间产生电场,从而可以在LISN阻抗上感应出位移电流与电压。当走线是在两个内层之间布线时,它可以显著降低这种耦合。不过,走线上方或下方的接地层存在小孔的情况下会大幅削弱改善的效果。这个结论令人十分意外:即使是PCB一个小区域上方存在的一个小孔也会显著降低改进效果。利用建议的仿真工作流程,可以非常直接地研究备选配置,例如:修改PCB的驱动与终端阻抗或修改其布局。

SIMULIA提供了一套先进的仿真产品组合,其中包括Abaqus、Isight、fe-safe、Tosca、Simpoe-Mold、SIMPACK、CST Studio Suite、XFlow、PowerFLOW等。SIMULIA社区是寻找SIMULIA软件最新资源以及与其他用户展开协作的最佳场所。作为打开创新思维和知识积累之门的钥匙,SIMULIA社区为您提供了您需要的各种工具,随时随地帮助您扩大知识面。

来源:达索系统