从三个角度理解,为什么结构振动总以低阶振动为主!

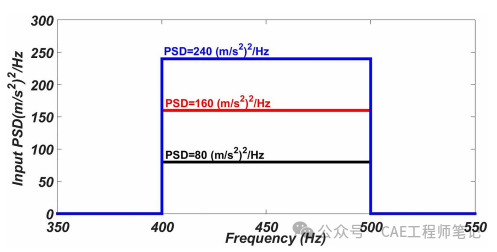

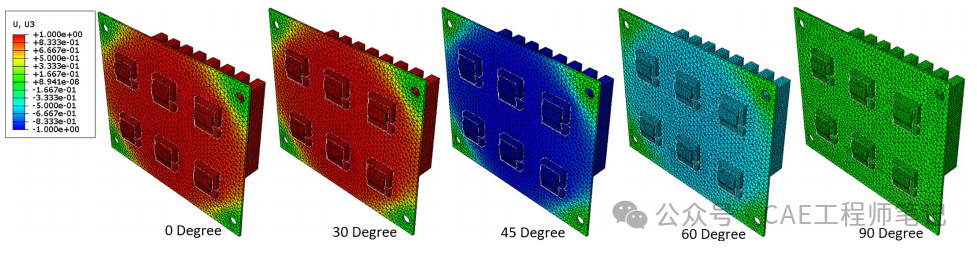

01背景笔者创作本文,是基于自己对振动问题的经验和理解,没有直接参阅相关主题的权威资料。如有错误荒谬之处,恳请大家批评指正!02导读在结构仿真模态分析中,相比低阶模态,高阶模态频率往往很难准确获取。主要是因为高阶模态对几何模型细节和连接刚度定义等都比较敏感。但这不太影响分析者解决振动问题,因为大部分情况下,结构振动的主要成分是低阶振动。那这就出现一个重要问题。为什么结构振动总以低阶振动为主呢?03激励自由振动是指结构受到初始激励之后的振动,受迫振动是指结构振动过程中一直承受激励。无论如何,我们谈论的结构振动,总是需要激励的。从激励的角度来解释为什么结构振动总以低阶振动为主!如果激励中缺少高频激励,那么结构振动自然也就缺少高频振动。举例来说,当高速电机的转速为10000RPM,对应工频(转动频率)也仅仅为167Hz。可以看出,高频激励确实不容易存在。04能量用简支梁振动举例来说,相同振幅下,高阶振动的势能(或者动能)远大于低阶振动。从能量的角度来解释为什么结构振动总以低阶振动为主!激发高频振动需要更多的能量。高频激励本来就不容易存在,高能量的高频激励则更少见。05阻尼阻尼机理非常复杂,阻尼类型也有多种,如下图所示。从阻尼的角度来解释为什么结构振动总以低阶振动为主!从上图的阻尼能(单位周期内阻尼的耗能)来看:粘性阻尼的阻尼能和振动频率成正比,并且振动频率越高,周期越短。所以单位时间内,粘性阻尼的高频振动耗能会远大于低频振动,即高频振动会很快衰减;迟滞阻尼和库伦阻尼等的阻尼能虽然和振动频率无关,但是振动频率越高,周期越短。所以单位时间内,迟滞阻尼等的高频振动耗能也会大于低频振动。06总结总结以上原因,从激励成分、激励能量、阻尼耗能三个角度都表明:结构振动总以低阶振动为主。当然笔者强调,并不是所有场景下都是低阶振动为主。在某些独特的问题中,高频振动往往是问题的主因,所以研究如何在仿真分析中得到准确的高频模态结果也是一个值得思考的方向。文章来源:华仿CAE来源:一起CAE吧