半导体仿真技术- 随机振动与封装可靠性分析

本文摘要:(由ai生成)

电子封装技术历经多个发展阶段,其可靠性对电子产品性能至关重要。焊点作为关键互连结构,其可靠性受到摩尔定律推动下的高密度化和高集成化挑战。焊点在服役时受到多种载荷影响,可能导致热疲劳和电迁移等问题。本文通过仿真分析发现,振动载荷方向对焊点可靠性具有显著影响,垂直于PCB的载荷条件下焊点可靠性最高。研究结果有助于优化电子封装设计,提升电子产品可靠性和寿命。

INTRODUCTION:电子封装可靠性

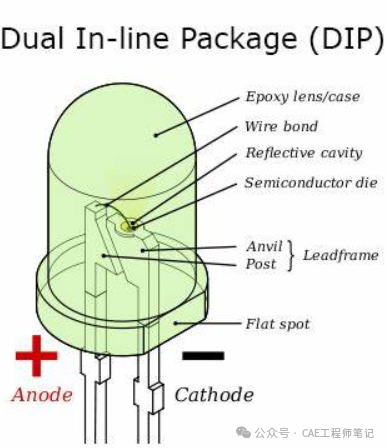

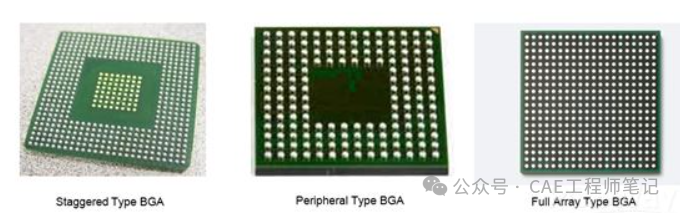

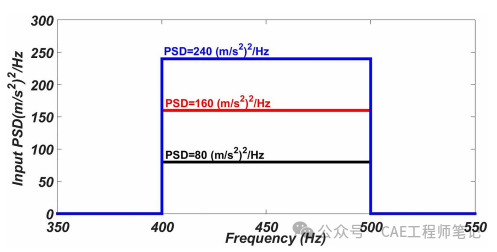

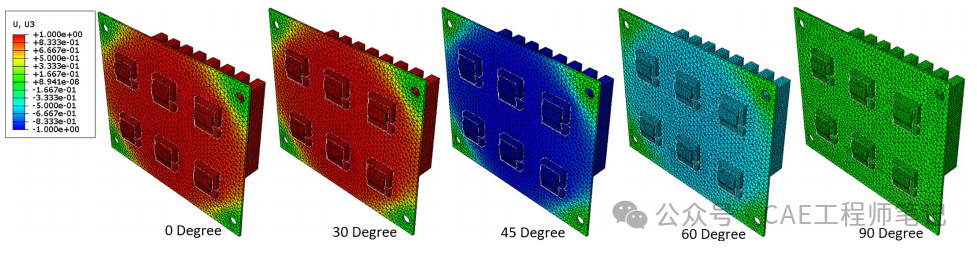

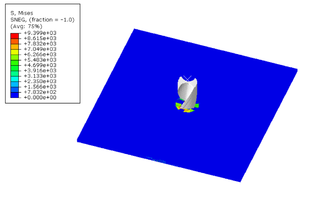

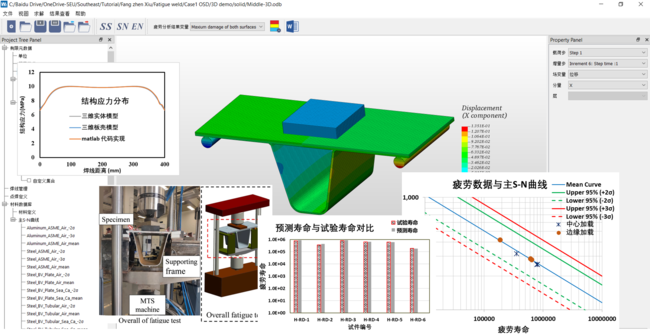

电子封装是一种将电子产品中各个功能单元连接起来的先进技术,它实现了芯片内外部电路的连接、芯片功率的输入输出。1947年世界上第一只晶体管正式诞生,这可以作为电子封装技术的起点。第一阶段为20世纪60-70年代。采用的是接线板焊接的方式,框架为电路板,芯片封装的形式以通孔器件和插件为主,双列直插式封装(Dual in-line package,DIP)为主要代表。这一阶段的封装基板面积较大,芯片的面积占比仅为10%~15%,是二维的封装形式。第二阶段为20世纪80年代。这一阶段主要是因为一种新封装形式的兴起,表面贴装技术(Surface mounted technology,SMT)。表面贴装技术是将扁平引脚分布在器件的两边或者四周,这种技术极大地改变了元器件和电子产品的面貌。第三阶段为20世纪90年代。随着各领域的发展需求,芯片的功能变得愈发复杂,带来的结果就是芯片的输入以及输出密度成倍地增加。原先引脚分布在芯片四周的形式由于引脚数有限根本无法满足高性能芯片的需求。在这种背景下,球珊阵列封装(Ballgrid array,BGA)和倒装芯片(Flip chip,FC)技术随之兴起。这种新技术与之前封装形式的区别就是,引脚转换为焊球的形式,而且不再分布在器件的四周,而是以阵列的形式分布在整个芯片的背面,这极大地增加了芯片的引脚数,使芯片能很好的满足当时的需求。球栅阵列封装器件由于其高互连密度、优异的电性能等优点,被广泛应用于军事和航空航天电子设备中。第四阶段为20世纪初。这时以芯片尺寸封装(Chip size package,CSP)技术为代表,CSP是以芯片尺寸或者比芯片稍大的尺寸作为封装尺寸,有效减少了封装尺寸,这迎来了微电子封装技术堆叠式封装的新时代,芯片占基板的面积已经高达70%~90%。封装工艺无论是在概念上还是外观上都发生了革命性的变化,从原来的封装元件概念演变成封装系统。焊点作为电子器件封装中的关键互连结构,既承接电信号互连,又承担机械连接,同时提供散热通道,因此,焊点的可靠性直接影响整个器件的可靠性。电子封装可靠性研究是一项重要的环节。在电子封装高速发展的历程中,始终存在着摩尔定律,集成电路上可以容纳的晶体管数目在大约每经过18 个月到24个月便会增加一倍。这就导致了处理器的性能大约每两年就会翻一倍,同时价格下降为之前的一半。半导体器件也确实不断地高密度化与高集成化,半导体器件的性能在不断地提高,器件数量不断地增加,电子产品的可靠性面临着更加严酷地考验。焊点是可靠性研究的重点关注部分。在电子产品中,芯片通过焊点实现与电路板的机械连接与电气连接。焊点服役时主要承受高温、冷热循环、强电压等载荷。高温载荷会导致焊点产生剧烈界面热扩散;芯片中材料的热膨胀系数往往存在差异,冷热循环载荷会导致焊点材料热膨胀系数不匹配,从而产生应力集中、热疲劳破坏等问题;强电压电流载荷可能引起焊点产生电迁移与热迁移,这会使焊点产生细微的裂纹,这些裂纹的不断扩展会让焊点发生断裂,最终导致电子产品失效;更需要注重的问题是如今焊点的尺寸在不断地微型化,微小焊点在受到多载荷时可能会发生多种应力叠加,产生全新的失效模式,导致电子产品的服役寿命大幅度缩短。电子产品在温度、振动/冲击等载荷下的失效率高达75%。本CASE重点研究了振动载荷的方向及其对焊点可靠性的影响。在CASE中,FEM模型是一个功率逆变器,包括六个MOSFET、散热器和PCB,如下图所示。振动载荷方向考虑了五种不同的方向。振动载荷方向选择与电路板表面垂直的0°、30°、45°、60°和90°角。下图展示了施加在电路板上的振动方向。仿真的第一步是计算系统的动态特性和固有频率。固有频率定义了模块在没有任何阻尼力的情况下振荡的频率。因此,如果自然频率出现在强制频率范围内,则振荡幅度将会增加。通过Block Lanczos和叠加方法获得一阶固有频率,如下图仿真结果显示了组件的动态特性,并计算出一阶固有频率为466.8Hz。在初步评估之后,将PSD施加到系统,并在接近固有频率的窄带随机激励中计算机械响应。然后,将随机振动载荷分析为PSD和应力均方根(rms)的函数。为了评估系统在输入机械载荷下的stress history,本CASE在研究应力特性时考虑了最大peeling stress的均方根值。如下图所示,对系统应力分布的初步分析表明,MOSFET与PCB之间的焊点是电子系统中最薄弱的部件。根据焊点中peeling stress的rms,在振动频率期间,焊料层的最外角承受最大应力。仿真分析结果还表明,振动输入的方向对焊料层上的应力集中起着至关重要的作用。当加载方向为0°(与PCB相切)时,焊料层在拐角处承受最大应力,而随着加载角度的增加,焊点中的应力急剧下降。焊料层拐角处应力的有限元结果表明,样品在0°振动下的最大应力是在90°(垂直于PCB)下加载的21倍。如下图所示,这是由于振动加载过程中的剪切应力造成的。承受垂直于焊料层的载荷的样品的剪切应力最小,而随着载荷角的减小,剪切应力的部分增强。因此,随着振动载荷角的增加,裂纹萌生和扩展的可能性逐渐变小。综上所述,在振动加载过程中,焊点的角部承受最大剥离应力。随着加载角的减小,peeling stress在焊料材料中的集中度增加。研究表明,这种现象是由于较低角度载荷下剪切应力的增加引起的应该注意的是,与我们考虑的封装相比,在更大的组件中,PCB弯曲会对应力分布产生显著影响,从而导致焊点可靠性的变化。