Cadence-Allegro-Sigrity介绍

本文摘要(由ai生成):

这篇文档介绍了 Cadence Allegro Sigrity 电源完整性和信号完整性解决方案,其中包括 PowerSI、PowerDC 和 OptimizePI 三款工具。这些工具基于 Sigrity 专利技术,提供了从芯片、封装到单板的完整电源和信号分析,帮助设计者解决电源完整性和信号完整性问题。主要功能包括全波电磁场分析、电源网络和信号网络阻抗提取、EMI/EMC 分析、电热协同仿真、自动优化电压调节模块感应线位置等。此外,还介绍了 OptimizePI 工具,它是一款基于 Cadence 的电磁场电路混合引擎的工具,结合专有的优化算法,可帮助用户快速得到最佳的电容波方案及布局方案。

Cadence Allegro Sigrity介绍

高科技企业开发复杂的芯片,封装和单板努力克服由于飞速增长的IC速度和数据传输速率联合引起的供电电压的降低,更高密度,越来越小型化的结构引起的电源完整性和信号完整性问题。同时,更高的I/O数目,多堆叠的芯片和封装以及更高的电气性能约束都使得IC封装物理设计更加复杂。

Cadence具有突破型进展的解决方案,基于Sigrity专利技术,解决这些设计挑战。该解决方案致力于完整的电源供电系统分析跨越了芯片,封装和单板;系统级的信号完整性(SI)分析,包含高速信号传输同步反转噪声和单个和多个芯片封装,最先进的 3D封装以及系统级封装(SiPs)的高级物理设计。

Power Integrity电源完整性

Cadence 电源完整性(PI)解决方案,基于Sigrity技术,提供signoff级别精度的PCB和IC封装的AC和DC电源分析。每个工具都能与Cadence Allegro® PCB 和IC封装物理设计解决方案无缝集成。

Sigrity PowerSI

IC封装和PCB设计快速准确的全波电磁场分析

作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。

Sigrity™ PowerSI®可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压超标等问题,从而帮助用户发现或改善潜在的设计风险。

PowerSI可以方便的提取封装和PCB的各种网络参数(S/Y/Z),并对复杂的空间电磁谐振问题产生可视化的输出。PowerSI能与当前主流的物理设计数据库如PCB, IC封装和系统级封装(SiP)进行无缝连接。

主要功能

• 为IC封装和PCB的电源分配网络(PDN)的可靠设计提供指导

• 可以分析板上任意结构的电磁耦合特性,为器件/去耦电容的放置位置以及过孔的排布提供依据

• 可以提取IC封装电源网络与信号网络的阻抗(Z)参数及散射(S)参数,研究电源的谐振频率以及输入阻抗,或研究信号的插入损耗及反射系数,为精确分析电源和信号的性能提供依据; 为时域SSN仿真提供可靠的宽带网络参数模型

• 分析整板远场和近场的EMI/EMC性能,全三维显示复杂的近场辐射水平,为解决板级的EMI/EMC问题提供依据

• 分析板上任意位置的谐振特性,找出系统在实际工作时电源平面上的谐振及波动特性,为电源的覆铜方式及去耦电容的放置位置提供依据

• 支持叠层以及其他物理设计参数的假定(What-if)分析,快速评估设计参数对系统性能的影响

• 基于专利算法的精确直流求解引擎(PowerDC),可支持从直流(DC)到宽频段的精确模型提取

• 与三维(3D)IC封装设计和板级设计工具无缝集成

优势与特点

• 专业的频域分析工具,致力于Package/PCB全面的信号完整性、电源完整性、EMI/EMC的分析,有10年的历史,经过数以千计的设计产品验证,成熟可靠

• 算法稳定可靠,即使对不规则的平面结构也能精确求解

• 提供智能的多CPU、多任务分布式计算能力,可以把一个大型的复杂任务分配给多个CPU或多台计算机同步完成,从而大大提高了仿真效率。

• 独特高效的电磁场分析技术使得PowerSI对多层电源地平面、大量的过孔和走线等复杂和规模巨大的封装和PCB设计依然能快速有效求解;

• 具有灵活多样的2D和3D fly-through等显示方式• 支持各种灵活的端口定义选项,允许用户自定义基于节点、器件、管脚、网络等方式产生端口

• 强大的SPICE语法支持能力

• 与各种ECAD数据库如Cadence® SiP Layout, Allegro® Package Designer, 和 Allegro PCB Designer ,以及Mentor, Zuken和Altium设计都有专门优化的接口

Sigrity PowerDC

确保可靠的电源供应

Sigrity™ PowerDC™应用于电热协同仿真,热点检查,低压大电流的PCB和封装产品电性能分析。

PowerDC针对于当前低压大电流的PCB和封装产品提供了全面的直流分析,并且集成了热分析功能,实现电热的混合仿真。通过PowerDC可以确保各器件端到端的电压降裕量,进而确保电源网络的稳定供应。PowerDC可以快速检测定位电流密度超标、温度超标的区域进而降低产品的风险。

PowerDC提供业界唯一的电源模块感应线自动优化功能,通过该功能快速实现当前设计电源的最优化。PowerDC流程化的自动规则检查功能,并结合可视化的选项与DRC规则检查,帮助用户快速提高产品性能。

特点

• 帮助用户确定直流压降,电流密度问题

• 自动优化电压调节模块(VRM)感应线的位置

• 定位引起系统风险的电流热点

• 检测并罗列不易发现的不满足要求的过孔和布线瓶颈区域

• 通过电热混合仿真充分考虑电热之间的相互影响

• 帮助用户确定在不增加风险的情况下减少平面层设计的可行性

• 实现对PCB和封装并可结合芯片级的信息进行分析

• 通过一系列可选的内容显示控制实现报告的自动化,并通过其中的拓扑模块图实现压降的快速分析

优势

• 便捷的流程化操作方式是专家级的用户或偶尔使用的用户的理想选择

• 业界唯一的电热混合仿真功能,使之能够获得电和热的相互影响的精确结果

• 高效的直流和热仿真效率,即使是大规模的PCB和封装产品也能快速实现直流和热性能的验证

• 电压调节模块(VRM)感应线自动优化的专利,相对常规的设计通常可以改善10-20%的性能

• 精确的算法,即使是针对复杂的多网络多平面结构也可得到准确的结果

• 全面的复杂结构支持,如:堆叠、多板仿真、常见的所有封装结构等

• 针对Cadence® SiP Layout, Allegro® Package Designer, and Allegro PCB Designer的流程

• 与Mentor, Zuken, Altium等PCB和封装布线文件都有良好的接口,并且能够AutoCAD的文件

Sigrity OptimizePI

基于性能成本的优化工具

Sigrity™ OptimizePI™是针对PCB和封装的频域仿真工具,通过前仿真和后仿真实现电容方案的选型和优化,进而提高系统或器件的性能。

OptimizePI是能够帮助设计者综合考虑PCB或封装的电源分配网络(PDS)去耦电容的性能和成本。

OptimizePI通常可以节省15%到50%的成本,通过分析可以确保系统或器件的PDS实现最佳性能。

OptimizePI基于Cadence的电磁场电路混合引擎并结合专有的优化算法,帮助用户快速得到最佳的电容波方案及布局方案。

特点

• 自动选择和放置去耦电容

• 减小PCB 和IC 封装中去耦电容的过设计

• 减小新老产品设计中PDS的成本

• 制定出高效的去耦电容的设计规则

• 重新获得不需要的去耦电容所占据的设计区域

• 动态评估PDS 成本和性能

• 结合PCB和封装优化PDS性能

• 创建最低成本、最佳性能的去耦电容放置表

• 确定EMI电容的数量和位置

优势

• 确保PDS 性能的基础上实现成本的降低

• 唯一一个高度自动化并综合考虑PDS性能和成本的工具

• 稳定精准的混合电磁场和电路分析技术

• 直观易于交互的可视化PDS性能分析

• 便利的前仿真后仿真设置

• 业界唯一的快速阻抗检查和EMI谐振检查功能

• 支持包括封装和PCB的大规模尺寸产品分析

• 针对Cadence® SiP Layout, Allegro® Package Designer, and Allegro PCB Designer的流程

• 与Mentor, Zuken, Altium等PCB和封装布线文件都有良好的接口,并且能够AutoCAD的文件

Sigrity OptimizePI

基于性能成本的优化工具

Sigrity™ OptimizePI™是针对PCB和封装的频域仿真工具,通过前仿真和后仿真实现电容方案的选型和优化,进而提高系统或器件的性能。

OptimizePI是能够帮助设计者综合考虑PCB或封装的电源分配网络(PDS)去耦电容的性能和成本。

OptimizePI通常可以节省15%到50%的成本,通过分析可以确保系统或器件的PDS实现最佳性能。

OptimizePI基于Cadence的电磁场电路混合引擎并结合专有的优化算法,帮助用户快速得到最佳的电容波方案及布局方案。

特点

• 自动选择和放置去耦电容

• 减小PCB 和IC 封装中去耦电容的过设计

• 减小新老产品设计中PDS的成本

• 制定出高效的去耦电容的设计规则

• 重新获得不需要的去耦电容所占据的设计区域

• 动态评估PDS 成本和性能

• 结合PCB和封装优化PDS性能

• 创建最低成本、最佳性能的去耦电容放置表

• 确定EMI电容的数量和位置

优势

• 确保PDS 性能的基础上实现成本的降低

• 唯一一个高度自动化并综合考虑PDS性能和成本的工具

• 稳定精准的混合电磁场和电路分析技术

• 直观易于交互的可视化PDS性能分析

• 便利的前仿真后仿真设置

• 业界唯一的快速阻抗检查和EMI谐振检查功能

• 支持包括封装和PCB的大规模尺寸产品分析

• 针对Cadence® SiP Layout, Allegro® Package Designer, and Allegro PCB Designer的流程

• 与Mentor, Zuken, Altium等PCB和封装布线文件都有良好的接口,并且能够AutoCAD的文件

Power-Aware SI

Cadence® power-aware信号完整性(SI)工具,基于Sigrity技术,提供Signoff级别精度的PCB和IC封装的SI分析.Sigoff级别SI精度对于比千兆赫兹更高频率的信号一定考虑信号和电源/地网络以及电流的回流路径.Cadence Power-Aware SI工具接口与Cadence Allegro® PCB 和 IC封装物理设计解决方案无缝的集成欲与创建完整的考虑电源设计和SI分析的解决方案。

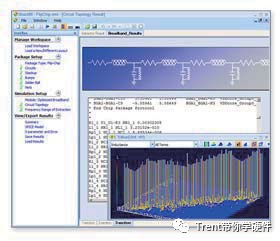

Sigrity Broadband SPICE

将网络参数转成SPICE电路

Sigrity™ Broadband SPICE®能够实现S参数的检查,修整,转换,将N端口的网络参数转成更高效的可用于时域分析的SPICE等效电路。

Sigrity™ Broadband SPICE®能够实现S参数的检查,修整,准确转换成SPICE等效电路转换。在保证高精度转换的同时,输出无源性的电路模型,使之能够用于HSPICE的瞬态仿真或者其他SPICE兼容的电路求解器,包括Sigrity SPEED2000™这个时域求解工具。

Sigrity™ Broadband SPICE®

Boardband SPICE可以导入散射参数(S)、阻抗参数(Z) 以及导纳参数(Y)等N端口的无源网络参数或者BNP格式的网络参数。Boardband SPICE输出具有良好收敛性的SPICE电路兼容模型。

特点

• 将网络参数转换成SPICE等效电路

• 实现频域模型到快速准确的时域模型转换的最有效的桥梁

• 创建从DC到全带宽的宽频带模型

• 准确模拟网络参数中的谐振点

• 创建包括IC封装、RF器件、PCB、电缆和接插件等对象的宽带模型

• 评估信号跨分割、信号回路不连接的应用情形

• 对于复杂的网络参数,创建高阶且稳定的模型

• 能够快速分析分析如SSO、电源地阻抗等问题

优势

• 一键式的转换就可以获得HSPICE或通用 SPICE兼容的模型

• 通过修剪S参数,减少瞬态仿真的问题并提高仿真效率

• 通过创建准确复杂的电路模型,改善SPICE仿真的收敛性和效率

• 软件自动转换能力结合用户的检查和设置确保准确修正原始数据的无源性问题

• 子电路的内部结构和阶数是软件根据网络参数的复杂度自动调节

• 灵活的流程可依据不同的仿真器产生不同的模型

• 支持Touchstone文件及更复杂的Cadence BNP文件

Sigrity Transistor-to-behavioral Model Conversion (T2B)

将总线仿真的效率从几天缩短到几个小时

精确快速的晶体管级I/O模型到行为级I/O模型转换工具,大大提高系统级时域仿真的效率。

Sigrity™ Transistor-to-Behavioral (T2B™) 是专门为精确的系统级仿真而开发的晶体管I/O模型转换工具。由于晶体管模型在时域仿真中效率低下,而传统的IBIS模型则不能精确模拟同步翻转输出(SSO)电源噪声对信号的输出影响;当前快速成长的总线仿真中迫切需要一种能精确模拟电源噪声的高效的I/O模型。这对高速总线的SSO验证分析尤为重要。

T2B将晶体管级I/O网表模型转换为保证精度的行为级电路模型,从而将传统的需要几天才能完成的总线仿真缩短到几个小时。T2B能产生标准的IBIS 3.2, 4.2和Power-aware的IBIS 5.0模型,以及更为精确的IBISPlus电路模型。其Power-aware特性能极大提高IBIS仿真中对电源噪声模拟的精度,而又相比于晶体管模型具有无可比拟的性能优势。所有的T2B I/O模型都能被信号完整性(SI)分析工具如Sigrity SPEED2000™,SystemSI™以及其他SPICE引擎如HSPICE支持。

主要功能

• 将晶体管级的模型转换成高精度的行为级模型

• 自动生成IBIS 3.2, 4.2 或者5.0规范的模型,还可以生成精度更高的模型

• 极大提高芯片/系统联合仿真的效率和能力

• 帮助确认SI/PI问题的根本原因并验证

• 生成用于SystemSI或SPEED2000进行总线仿真分析的power-aware行为级模型

• 时域仿真分析模板用于行为级模型精度与原始晶体管模型精度比较验证

• 使得包含所有总线的芯片-封装-系统模型的联合仿真流程成为现实可能

优势与特点

• 业界唯一自动产生IBIS 5.0 power-aware模型的转换方法

• 业界广泛使用的Sigrity SI/PI仿真工具流程的一部分

• 模型转换流程里包含精度验证

• 高度自动化流程并且对熟悉IBIS语法的工程师来说简单易用

• 包含所有IBIS BIRD95/98中定义的power-aware效果

• 使得可能花费几周时间进行的全总线仿真流程成为现实

• 生成的模型可以直接应用于SPEED2000和SystemSI

Package Design/Assessment

封装设计/评估

Cadence®封装设计和评估工具,基于Sigrity技术,提供IC封装设计,分析和模型提取能力-可以和Cadence SiP Layout 和Allegro® Package Designer转换数据.评估能力允许您准确快速评估信号和电源完整性问题的可行性。模型提取功能提供独特的全封装模式提取,精度达到多千兆赫兹频率范围。

Sigrity XtractIM

10倍以上的封装模型提取性能

Cadence®封装设计和评估工具,基于Sigrity技术,提供IC封装设计,分析和模型提取能力-可以和Cadence SiP Layout 和Allegro® Package Designer转换数据.评估能力允许您准确快速评估信号和电源完整性问题的可行性。模型提取功能提供独特的全封装模式提取,精度达到多千兆赫兹频率范围。IC封装的RLC电路模型提取和评估,具有同类工具10倍以上的速度优势和无可比拟的全波精度,支持独一无二的优化宽带多阶电路模型。

Sigrity™ XtractIM™ 是专用的IC封装模型提取和分析工具,而IC封装模型对于系统级的信号完整性(SI)和电源完整性(PI)的精确分析尤为重要。相比较于同类工具,XtractIM的IBIS RLC电路模型或宽带SPICE电路模型提取都具有无可比拟的性能优势(通常快10倍以上)。

XtractIM 基于全波仿真算法提供无可比拟的宽带电路模型,其优化的多阶电路模型为用户提供独一无二的精度和高度压缩的模型大小。独特的封装模型电性能评估引擎使用户可快速发现和定位潜在的设计问题,强大的封装结构(如单芯片封装、多芯片封装MCP以及系统级封装SiP等、Flip-chip/Wirebond封装等)支持能力使得用户可快速提取全封装或部分网络的电路模型。

主要功能

• 为系统级分析提供IC封装设计指导和精确验证模型

• 产生耦合的标准IBIS RLGC电路模型

• 产生Pi-或T-电路格式的单阶SPICE RLGC模型

• 产生优化的宽带多阶SPICE电路模型

• 支持封装结构电性能的评估和检查,支持RLC电参数的可视化显示

• 支持单芯片或多芯片封装(MCP)设计,如Flip-chip,Wirebond, BGA以及Leadframe

• 支持全封装或有限网络的电路模型提取

• 支持系统级信号完整性(SI)/电源完整性(PI)分析

优势与特点

• 界面友好,易于使用,尤其适用用封装设计人员和新手

• 比同类工具的RLC模型提取通常快10倍以上

• 三维全波引擎保证其精确的模型提取能力

• 广泛的IC封装和系统级封装(SiP)支持接口

• 独特的封装模型电性能评估和图形化显示能力帮助用户快速评估潜在的设计风险并加以避免

• 灵活的Pin-Group选项使用户可自由掌握模型规模;支持完整封装设计的全模型提取,支持无源器件模型的自由链接

• 支持非对称Pi-或T-电路模型拓扑,精确模拟信号, 电源和地之间的相互耦合

• 支持宽带SPICE电路模型提取,其全波仿真引擎确保电路模型可验证的仿真精度

• 支持可压缩的宽带电路模型(通常是S参数模型大小的2%左右),大大提高时域仿真的效率

• 灵活的2D/3D显示模式, 表格化的结果输出和打印

• 优化的Cadence® 封装设计工具接口,支持Mentor 、Zuken等封装设计数据库

SPEED2000时域分析工具

现今第一个也是唯一一个可以对整板级EMI/EMC进行时频域结合电磁仿真分析的工具,让每一个工程师易用、流程化的轻松应对复杂的电磁问题,是真正的系统级解决方案。

SPEED2000用于电子封装和印制电路板的电源和信号完整性分析工具。它内核集成了电路仿真器,传输线仿真器以及一个快速、专用的仿真复杂对象如多层芯片封装、多芯片模块,以及多层印制电路板中的电磁场的电磁场仿真器。

• 高速信号(非常好的支持GHz以上信号仿真)网络的时域波形分析

• 电源/地噪声的实时纹波分析和空间分布分析

• 板级的EMI/EMC分析

• 自动生成详细的分析仿真报告

Co-Design

Sigrity Co-Design产品弥补了Cadence® SiP codesign解决方案,提供早期系统样机研究和联合分析的功能,他们能在非常短的时间周期内按照系统优化结果调整chip-package-board计划并最大优化性能。这些产品的结果和输出可以作为物理实现的开始。

Sigrity相关产品:

Sigrity PowerSI

先进的信号完整性,电源完整性及EMI解决方案。支持整个IC封装和PCB的设计S-参数模型提取,及强大的频域仿真功能。

Sigrity PowerDC

IC封及PCB设计的高效的DC解决方案的,支持电/热协同仿真,以最大限度地提高准确度。迅速且精确的定位IR Drop和当前的发热点。自动搜寻最好的遥感的位置。

Sigrity OptimizePI

自动化PCB及IC封装的AC频域解决方案。支持前和布局后去耦方案,确定阻抗的问题,支持建议EMI去耦电容的摆放位置。优化的基于性能或成本,及其他的去耦方案。

Sigrity SPEED2000

完整的PCB /封装布局基于时域EM的信号完整性仿真工具,同时支持电源完整性和EMI分析。能够用于高效准确的对布局设计进行检查和调试。

Sigrity SystemSI

针对于高速芯片到芯片的全面及自动化的信号完整性系统设计,准确的仿真评估环境。以确保并行总线,串行链路接口的可靠实现。

Sigrity Broadband SPICE

S参数的检查,调整及提取的组合工具,能够转换N端口的网络参数,用以等效SPICE的兼容电路,进行时域分析。

Sigrity Transistor-to-behavioral Model Conversion (T2B)

高效的晶体管级别的模型转换工具,可以创建SSO及其到类型的精准模型。其模型的运行速度,比用原来晶体管级模型,提高一个数量级。

Sigrity XtractIM

高效快速的IC封装RLC提取和评估解决方案,有选项来生成高度精确的宽带模式。支持范围广泛的封装类型,包括BGA,SIP,及LEADFRAME设计。

Sigrity OrbitIO Planner

协同设计解决方案,加速prototyping and pad ring planning in single/multi-die封装规划。支持Flip-Chip,WrieBond 及RDL的工艺,并且行业标准数据内嵌在IC,封装及PCB工具中。

Sigrity XcitePI

完整的芯片的电源完整性解决方案,针对芯片/系统协同仿真。支持早期的芯片的电源规划,I / O和核心驱动模型提取,支持时域及频域仿真。