如何全面地考虑电子产品板级热仿真问题

印刷电路板(Printed Circuit Boards,以下简称PCB)是由绝缘介质(FR4)与铜进行层叠的多层基板,是现今电子产品中用于电子元器件内电气连接的重要载体。各种芯片、元器件焊都需要在PCB上进行连接,形成板级电路。

板级产品设计时需要考虑到电可靠性与热可靠性。电可靠性包括功率及信号完整性,功率与信号完整性的设计会引出热损耗的问题,因此我们需要同时去评估热可靠性,之后两者之间会进行一个设计的迭代,最后得出可靠的设计结果。

在这里我们主要以ANSYS Icepak与SIwave为载体,讨论一下使用仿真去评估热的问题。

发热原因

■ PCB中,由于铜线的细小结构会存在较大的电阻,过孔处也会有较大的电流密度的聚集,加上错综复杂的排布,使得电流过载时产生难以预料的过热点。

■ 另外,布线产生的焦耳热与功率器件发热的叠加效应也是使得电子产品热失效/烧毁的原因之一。

电流过载时引起线路的烧毁

热评估方法

传统的板级热仿真会使用电子元件的功耗及其等效的PCB导热系数去做热评估,但是现在可以更加精确快速地完成设计的仿真评估。

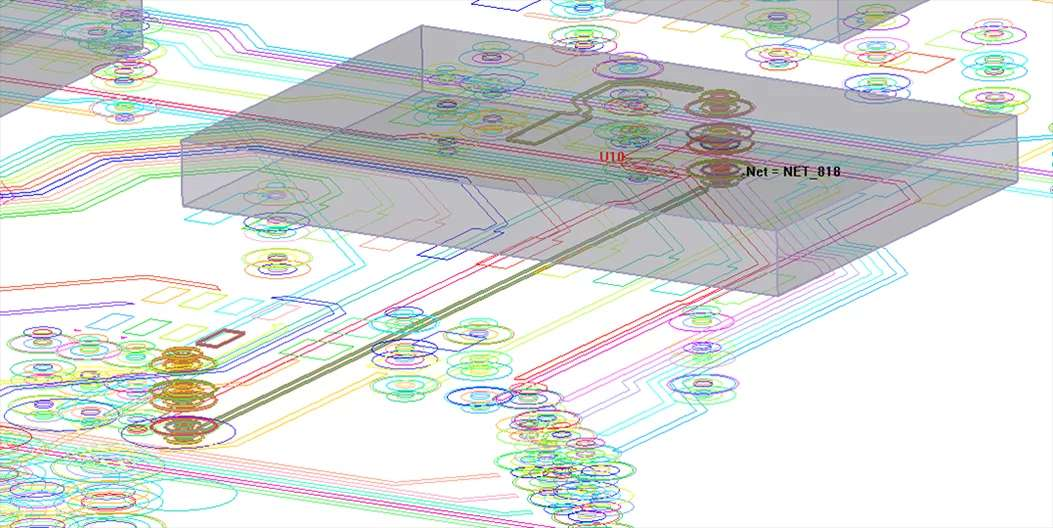

在ANSYS Icepak中,我们可以使用ECAD(PCB layout设计数据文件)对PCB各层的布线/线路分布及其过孔进行描述,并且计算出各层的导热系数分布,以此来精确地考虑铜材质的线路与过孔的分布,对PCB上焊接的电子元件散热效果的影响。

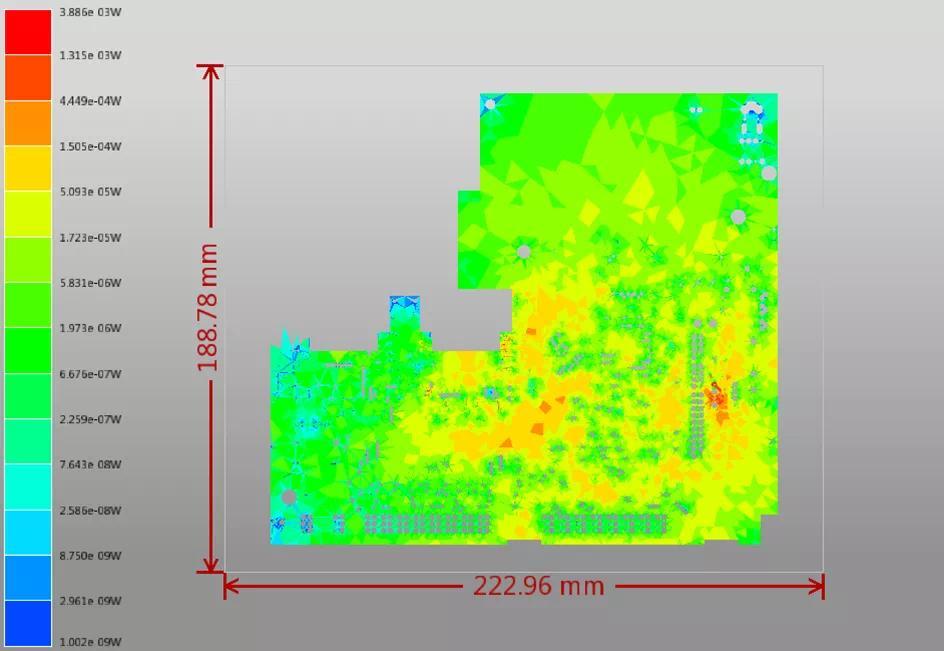

ECAD导入后的PCB模型

对于线路和过孔的考虑

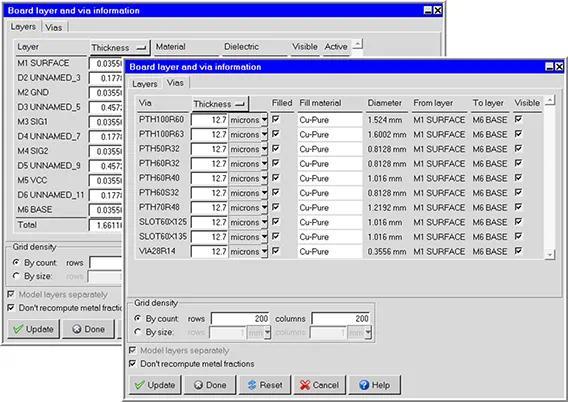

PCB各层layer根据ECAD计算的导热系数

可编辑修改ECAD中对layer与via的数据

与此同时,我们还需要考虑PCB线路的焦耳热产生的影响。

对于电热耦合的焦耳热计算,传统方法是利用3D实体来计算(例如母线Busbar)。但是由于PCB布线的几何相当细小,而且焦耳热的计算在导体边界对网格均一性要求较高,使用传统方法计算焦耳热时需要生成大量的网格,并且对于较细小、形状复杂的布线网格的质量控制较难。

n

对PCB线路进行实际网格的划分需要大量小尺寸网格

传统的计算方法不但需要大量的计算资源,还拉低了仿真计算的效率。因此,针对PCB线路的焦耳热,我们可以使用SIwave-Icepak耦合的方式去计算。

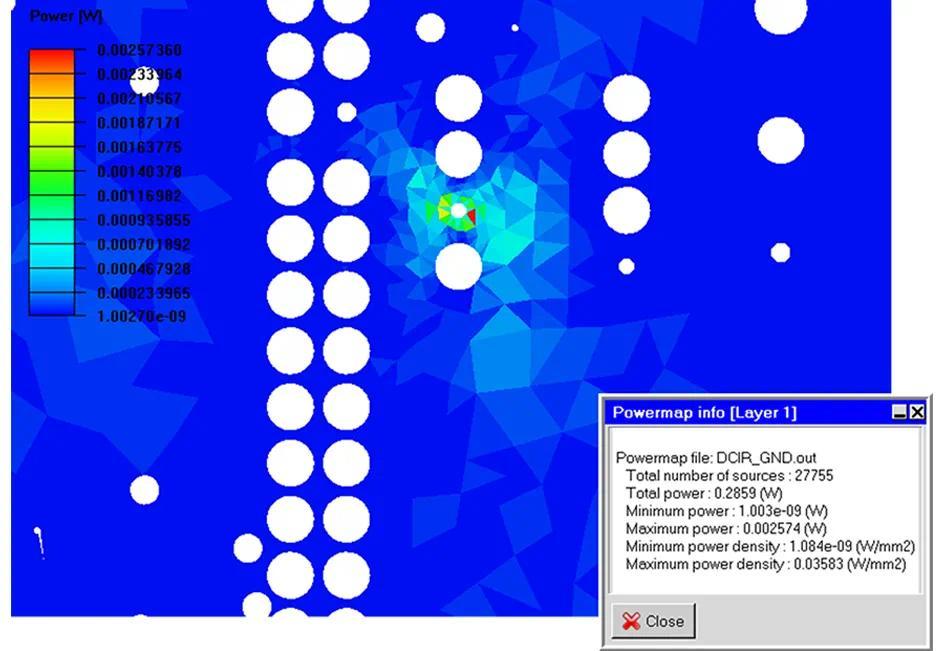

■ SIwave能够对PCB上的线路加载激励条件进行DCIR drop计算,获得不同工况下PCB上各层布线的焦耳热分布。

■ Icepak利用焦耳热分布数据的映射进行进一步的板级热仿真,评估在不同的工况下,PCB上铜线的焦耳热和电子元件发热共同作用时的温度布状态。在ANSYS SIwave中输出基于计算网格的焦耳热功率分布数据,在Icepak中使用Block或者PCB Objects,以SIwave Profile的方式导入,功率数据将直接映射并插值到Icepak的计算网格之中(相比于之前在Icepak中使用2D heat source构成power map的方式,这种方式几乎不怎么占用计算资源)。

SIwave焦耳热功率分布

Icepak中的焦耳热分布(集中区域)

双向耦合方法

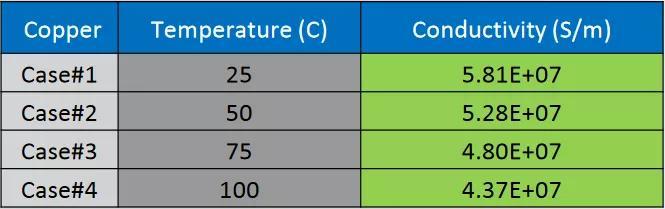

常用导电材料的电导率——以铜为例,会随温度的改变有较大的变化,继而会产生焦耳热功率的变化。

单纯的单向耦合计算无法考虑到温度对材料物性的影响会与真实状况有较大差异,因此在这一方面我们可以用双向耦合的方式来解决这个问题。

铜的导电率随温度的变化s1= s2/ [1 + a * (T1–T2)] (a= 0.0040)

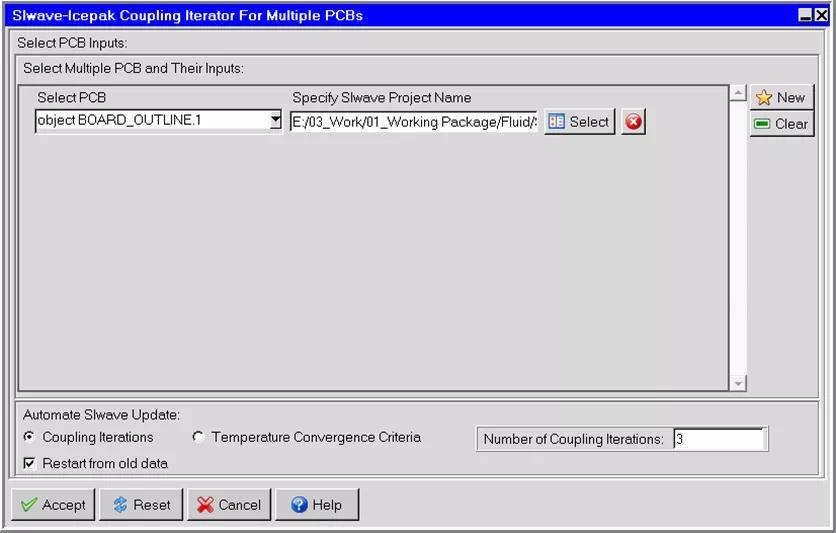

Icepak-SIwave的双向耦合可以通过手动进行文件输入输出的方式实现,也可以使用Icepak中已开发的宏来自动进行迭代。

SIwave输出功率分布数据给Icepak,Icepak再将进行计算之后的温度场反馈给SIwave,以此来更新该温度分布下线路材料的导电率分布。一般来说,这样计算迭代3到4次将会得到耦合计算收敛的结果。

Icepak-SIwave双向耦合迭代宏

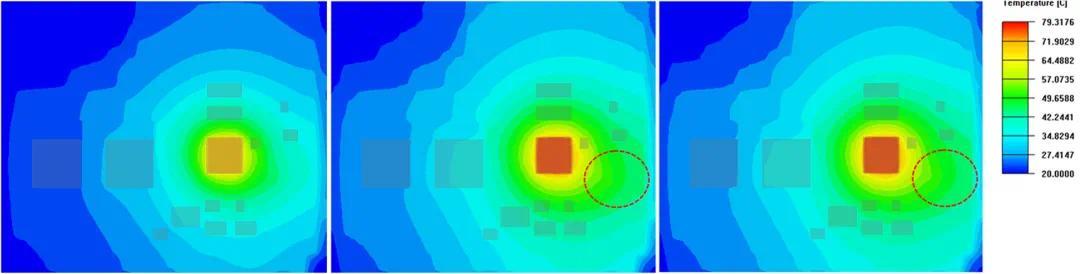

通过耦合迭代的结果,我们能够明显看出:铜线的导电率随温度降低而发生变化,继而导致发热元器件与局部PCB温度上升。

三次迭代中温度的变化云图,能够看到PCB线路的发热与周围温度互相影响的结果。(本次case中在双向迭代与否对比时最高温度有9.9%的差异存在)

总 结

板级的散热可以通过以上方法来进行仿真模拟,利用ANSYS Icepak-SIwave的双向耦合技术可以完整考虑到PCB的布线导热率分布、铜线焦耳热及其温度对导热率的影响,并且能够快速得到与真实情况最为相近的结果用于评估发热。

■ 当然,我们也不排除在研发前端没有EDA文件,只能等效近似地去做热仿真的情况,但是在后期设计完成时,也是一样可以利用此方法进行详细的验证工作。

■ 同样的,在Icepak中封装也可以用相似的方法进行详细的建模仿真,在这里就不多加介绍了。