让CST告诉你高速差分信号为什么要进行等长匹配

高速差分信号的等长匹配对于电磁干扰(EMI)起着至关重要的作用。

首先,等长匹配可以减少信号的时延差异,这对于高速差分信号的传输非常重要。当信号传输线长度差异较大时,传输线上的信号到达时间存在差异,可能会导致相位失配,从而引发相互干扰和串扰现象。这种干扰可以通过等长匹配来抑制,确保差分信号在接收端同时到达。

此外,等长匹配还能对抗EMI干扰。EMI是指电磁能量通过电磁波的形式干扰电子设备的现象。当差分信号传输线存在不匹配时,由于信号的时延差异,信号之间的电流和电压差异也会加剧。这可能导致更强的辐射和敏感性,使系统更容易受到外部电磁干扰。通过保持等长匹配,可以减少这种电流和电压差异,从而降低对EMI的敏感度。

因此,等长匹配在高速差分信号传输中起到了重要的作用,不仅可以提高信号的传输质量、减小串扰,还能减少对EMI的敏感性,从而提高系统的可靠性和抗干扰性能。

今天小编通过CST来谈一谈高速差分信号为什么要进行等长匹配。本文只谈EMI,不谈信号完整性。信号完整性后续会讲到。

仿真实例以DDR3的其中一对DRAM_DQS信号为例,它是差分信号。

DDR全名为Double DataRate SDRAM ,简称为DDR。DDR3理论上速度可以支持到1600MT/s。

DDR3的工作电压1.5V,参考电压0.75V,对于DQS信号的差分对等长匹配的要求是不大于5mil。

如图,DRAM_SDQS_P走线长度558.32mil, DRAM_SDQS_N走线长度是558.66mil

如图激励一个电压幅值为1.5V,信号频率为800MHz的差分信号,先仿真差分等长匹配好的情况,再分别仿真DRAM_SDQS_N增加40mil,80mil,120mil的信号和电场强度。

首先,来看一下在原模型基础上增加40mil的微带线,和原仿真结果的对比。

差分信号的开关变化是位于两个信号的交点,其电压与基准电压偏差0.09V。

整体电场强度变大,最大电场强度增加1倍。

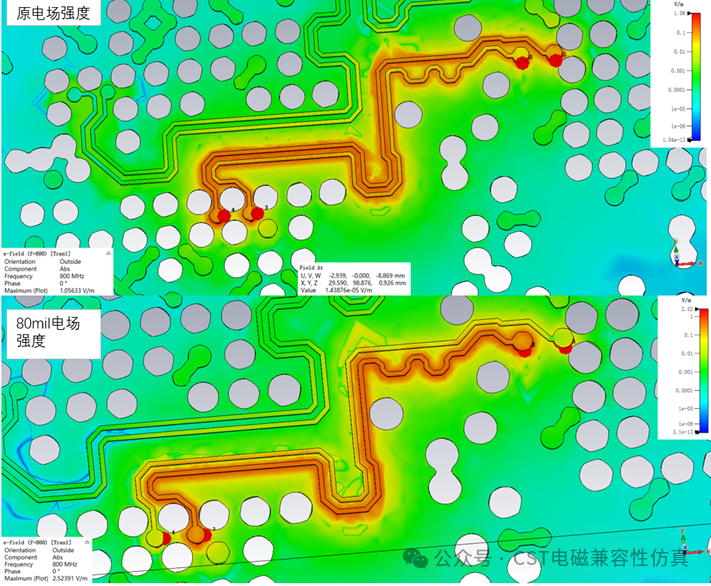

然后,在原模型基础上增加80mil的微带线,和原仿真结果的对比。

差分信号两个信号的交点电压与基准电压偏差0.17V。

整体电场强度变大,最大电场强度增加2.8倍,

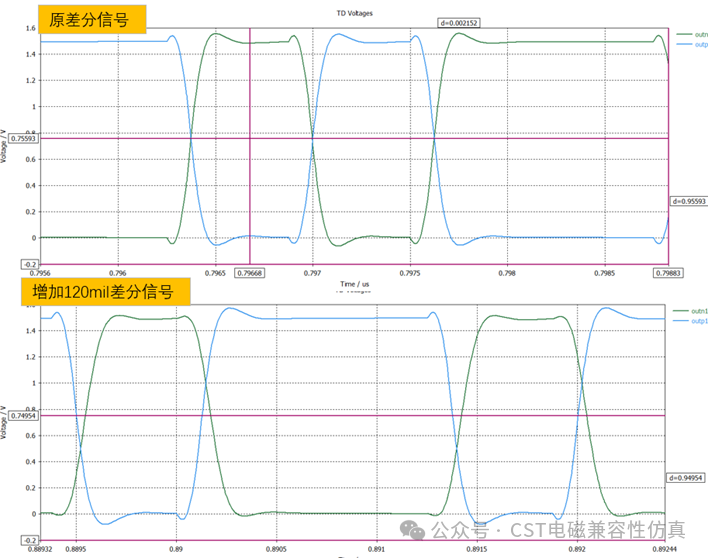

再次,在原模型基础上增加120mil的微带线,和原仿真结果的对比。

差分信号两个信号的交点电压与基准电压偏差0.26V。

整体电场强度变大,最大电场强度增加4倍

最后,增加一个probe,看一下PCB正上方的辐射,如图

其仿真结果如图:

很明显,差分信号走线长度差越大,辐射场强就越大。

总结:

在差分信号传输中,等长匹配是为了确保信号在传输过程中同时到达接收端,从而减少信号的相位失真和串扰。等长匹配可以一定程度上减小共模干扰的影响。当差分信号的传输线长度不匹配时,信号在传输过程中可能会出现相位失配,导致差分模式和共模模式之间的转换,使得共模噪音更容易进入信号传输通道。而通过等长匹配使差分信号同时到达,可以减小差分模式与共模式之间的转换,从而减小共模干扰对信号的影响。

因此,通过等长匹配可以降低差分信号传输中对共模干扰的敏感度,提高系统的抗干扰能力,从而确保信号传输的稳定性和可靠性。综上所述,高速差分信号的等长匹配在减小共模干扰方面发挥着重要作用。