版图设计

版图是包含集成电路的器件类型,器件尺寸,器件之间的相对位置以及各个器件之间的连接关系等相关物理信息的图形,这些图形由位于不同绘图层上的图形构成。

版图工程师的职责包括:芯片物理结构分析,逻辑分析,建立后端设计流程,版图布局布线,版图物理验证,联络代工厂提交生产数据。

版图设计方法(从自动化程度划分):

1.全自动版图设计:

利用计算机辅助设计工具以及电路的门级网表自动生成版图的设计方法。

全自动版图设计的步骤:

①准备阶段:详细了解版图库,一个完整的库包含电路仿真和综合以及版图设计使用的数据,版图设计的库主要包括:布局布线时需要使用的LEF文件和TLF文件, 版图验证时需要用到的库中单元版图数据文件和版图验证命令文件。拿到电路设计人员的门级网表后,要首先检查一下网表文件的内容,是否出现各种错误;在进行自动布局布线时,需要进行时序分析和时序优化,操作前需要前端设计人员提供时序约束(Timing Constraint)文件(GCF文件)。

②数据输入:在自动布局布线开始阶段,首先将库文件,门级电路网表文件和时序约束文件读入自动布局布线的EDA工具中编译。

③布局规划:布局规划阶段根据门级网表确定芯片的形状(高度宽度之比),大小,放置输入输出单元,放置各个模块,布置电源线。

在保证布线成功前提下尽可能缩小芯片面积。

布置电源线时,通过简单估算芯片功耗,由功耗估算最大工作电流,再知道单位宽度金属允许流过的最大电流,就可以知道需要布的电源线的宽度,需要留一些余量。

④自动布局:根据电路功能,性能,以及几何要求等约束条件下,EDA工具自动将各单元放在芯片适当的位置上。建立时钟树系统是自动布局布线重要的一环。布局完成后还需要优化布局。

⑤布线:自动布局完成后,进行时钟树的布线和其他信号线的布线。布线是指在满足工艺规则和布线层数限制等约束条件下,根据电路逻辑关系将各个单元之间以及各单元和输入输出之间用金属连线连接起来,并尽可能保证芯片面积最小。

⑥时序分析以及布线后优化:时序分析正确说明布线成功,时序分析依据的条件就是时序约束条件,如果时序分析结果不满足要求需要对布线进一步优化。

⑦版图验证:主要包括DRC(设计规则检查)和ERC(电学规则检查)以及LVS(电路图和版图一致性检查)。

⑧数据输出:版图设计完成后,输出GDSⅡ文件,交付给生产厂家进行掩模版生产。

2.半自动设计

在计算机上利用符号进行版图输入,符号代表不同层版图信息,再通过自动转换程序将符号转换成版图。

3.人工设计

主要应用在模拟电路版图,版图单元库设计,全定制数字集成电路设计中。

下面先了解一下CMOS制造流程:

具体过程参见这里:CMOS工艺基本流程

关于版图中的绘图层

以CMOS工艺为例,主要分为N阱层,有源区层,多晶硅栅层,N选择层,P选择层,接触孔层,通孔层,金属层,文字标注层,焊盘层。

Note:

(1)N选择层和P选择层:

MOS晶体管的有源区是通过将N型或P型杂质离子注入到选择层掩膜定义的衬底区域形成的,所以选择层定义的是覆盖有源区的区域。N选择层和有源区共同构成了扩散区(也称为N+)。

(2)接触孔:

**有源区的接触孔用来连接第一层金属和N+或P+区域,有源区面积允许下,尽可能多打接触孔可以降低等效电阻;

**多晶硅的接触孔用来连接第一层金属和多晶硅栅极;

**通孔(Via)用于金属层之间连接,面积允许条件下尽可能多打通孔;

**接触孔和通孔形状都是正方形;

**接触孔只有一层,通孔有多层,第一层金属与第二层金属之间的通孔记为V1,以此类推。

版图设计规则

概念:用特定工艺制造电路时所使用的物理掩模版图需要遵循一套几何图形排列的规则,这就是版图设计规则。

**分类:**Lambda版图设计规则 和 规整格式设计规则。

Lambda版图设计规则:在一般版图设计工具中各网格最小单位以Lambda计,Lambda的大小一般是工艺最小尺度的一半,也就是说大部分的尺寸都按照Lambda的整数倍来计。

规整格式设计规则:主要以微米为单位,也叫做自由格式,各尺寸之间没有必然的比例关系,可以提高每一尺寸的合理度,但也增加了设计难度。

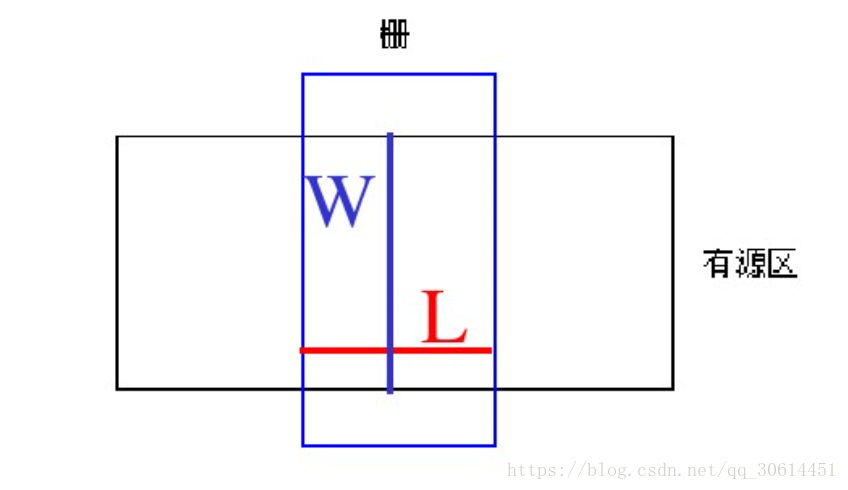

栅和有源区的重叠部分定义器件的尺寸,重叠之外的区域对尺寸没有影响。

基本设计规则包括:

线宽规则:版图中多边形的最小宽度,防止线宽太窄出现断路;

最大(最小)尺寸限制:多边形的宽度或长度不能太大也不能太小,一般针对接触孔和通孔;

间距规则:多边形之间的最小距离,避免两个多边形之间形成短路;

包围规则:一层与另一层线条之间交叠并将其包围的最小尺寸,主要用于不同层之间需要进行连接,该规则可以保证有效的连接;

交叠规则:两层之间交叠的最小尺寸;

最小面积规则:满足以上基本要求的前提下,尽量保证版图面积最小。

器件的两个关键尺寸就是如图的栅极的长度L和宽度W。

关键参数:

最小宽度(minWidth):封闭几何图形内边之间的距离

最小间距(minSep):几何图形外边界之间的距离

最小交叠(minOverlap),分为两种:一几何图形内边界到另一图形外边界的距离(overlap);以几何图形内边界到另一图形内边界的距离(extension)。

版图验证:

设计规则检查(DRC):根据上述设计规则进行检查;

电学规则检查(ERC):天线规则检查,非法器件检查,节点开路,节点短路,孤立接触孔;

版图寄生参数提取(LPE):从版图中提取到器件的参数,器件之间连接关系还有寄生电阻与电容,产生一个网表文件,从而可以恢复出电路图,和原电路图比较,查找错误。工具:Mentor公司的xCalibre

电路图与版图一致性检查(LVS):通过EDA工具分别从电路图和版图中提取出网表文件,然后对两者进行比较,常用工具就是Mentor公司的Calibre LVS工具。

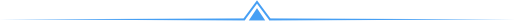

CMOS晶体管的版图

有源区外是一层反向扩散区,对于N阱CMOS工艺,衬底是P型低掺杂,PMOS管做在N阱内,此时PMOS有源区外再加一层P Selector层。

**NMOS俯视图

**PMOS俯视图

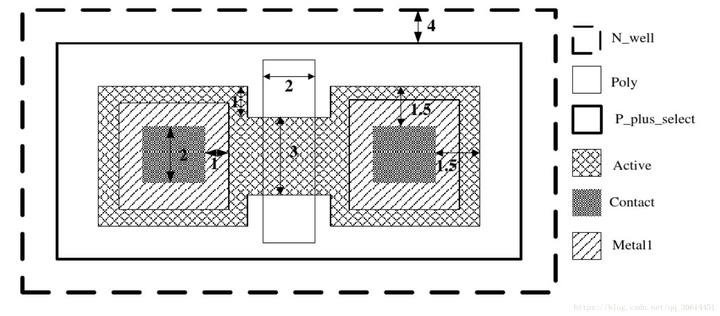

**多指结构MOS晶体管版图设计

导电沟道宽度过大,会使栅极电阻较大,一般可以通过拆分将一个晶体管变成多个晶体管的形式,而且拆分后的晶体管栅极电阻大大减小,如果均分成n个小晶体管,n个晶体管并联后形成的晶体管栅极电阻将是之前一个晶体管的1/n2.

对于上述拆分,观察版图可以知道,将偶数位的晶体管的源极和漏极调换(mos管源极和漏极是相同的),相邻晶体管的源漏可以共享,从而减少版图面积。

拆分之后晶体管的尺寸主要由三个参数:w(拆分后小晶体管的宽度),晶体管长度L,拆分数目N决定。对于拆分成6个小晶体管的6指晶体管来说,w如果是0.48um,相当于大晶体管的W是2.88um。

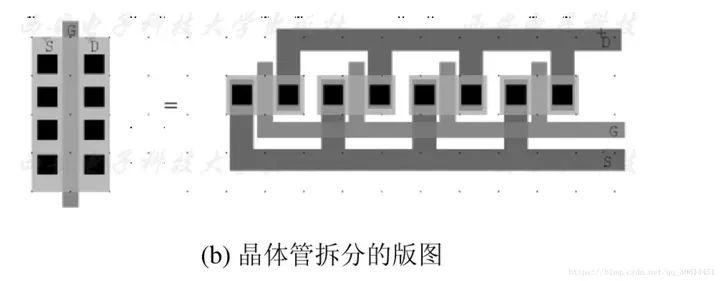

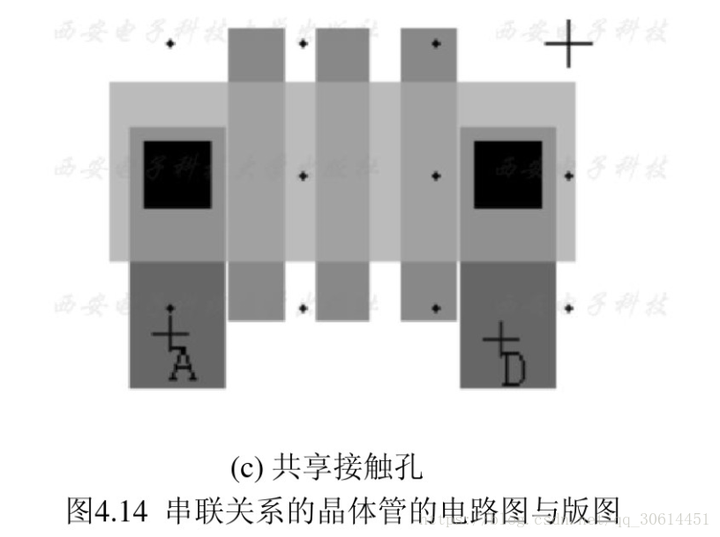

**串联晶体管的版图设计

对晶体管之间的串联,相邻晶体管的源漏可以共享,而且如果电路图中没有与其他器件相邻的话,共享区域的接触孔也可以省略,从而减小版图面积。

**并联晶体管的版图设计

并联关系的晶体管分为两种:

@两个管子只有一个端连在一起:

**器件布局对电路影响

器件放置的位置和方向对电路性能有很大影响。

对于两个要求相互匹配的器件一般要放在一起,以减少周围电路的环境对二者的差异影响;

器件摆放方向的影响源自于工艺处理中的各向异性。器件晶体管的宽长比对电路性能影响较大,而晶体管的宽长比受影响于多晶硅栅的长和宽,多晶硅栅通过刻蚀得到,刻蚀一般是各向异性,器件摆放方向不同刻蚀后得到的多晶硅栅的长和宽会不同,导致不匹配。

** 器件本身设计对电路性能影响

对要求匹配的器件,进行布局时一般把这些器件围绕一个中心进行放置,称为共心布局,如下图:

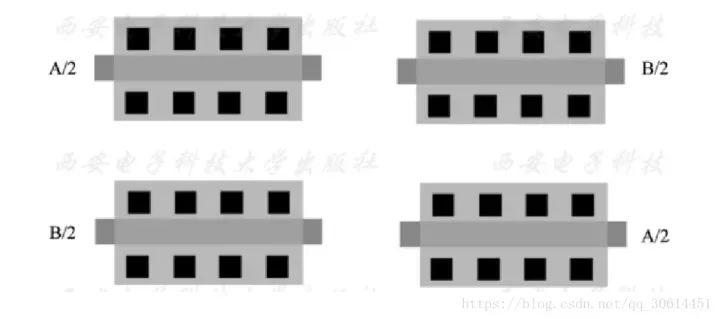

如果要求匹配的器件只有两个,可以采用四方交叉方法,就是将一个晶体管一分为二,再通过共心点的对角线放置,如下图:

也可以采用简单四方交叉,拆分后的晶体管按照A-B-B-A放置,如下图:

但是考虑到匹配问题,中间的两个晶体管与上下的两个晶体管所处的环境是不一样的,工艺处理带来的偏差也会不一样,A和B将会不匹配,此时,可以考虑在上下再各放置一个虚设器件,该器件对电路逻辑功能无影响,主要用于提高AB器件的匹配性。

END