高速光探测器仿真总结(二)

本文摘要(由AI生成):

文章主要介绍了光探测器的等效电路模型,包括载流子的渡越时间、芯片的寄生RLC参数等,并讨论了这些参数对探测器响应度和带宽的影响。同时,文章还提到了ANSYS电路仿真软件中自带的PIN PD电路模型,并指出该模型存在一些问题,建议读者自己搭建电路。

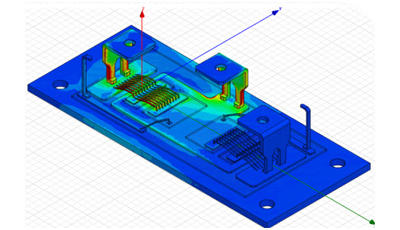

前面文章稍微总结了下高速光探测器仿真的总思路,完整的场路结合仿真是应该做的,同时也要对仿真结果进行分析,从仿真得到的眼图中的ISI和jitter,评估出由于封装和PCB走线引起的灵敏度劣化程度,最终来预算整个ROSA器件的灵敏度。

在实现场路结合仿真之前,需要完成光探测器(PD或APD)的基础功能分析,即如何实现光电(OE)这个转换过程,大家应该知道,目前的ANSYS electronics desktop,是不支持光电协同仿真的,只支持纯电磁场和电路的仿真,那么要实现OE的转换,就要另寻出路,除非有更强大的光电协同仿真软件出现。

在高频信号分析过程中,一些物理器件比如Laser 、photodiode以及EA chip等,都会用小信号等效电路模型(small-signal equivalent circuit model)来模拟这些器件的行为,通常是S参数以及眼图等,这些小信号模型仿真出来的S参数和眼图,应该能够跟实际测试的S参数和眼图非常接近,同时调整电路中某个阻容件的值,仿真出来的曲线变化规律与器件的实际行为表现也一致,这样就可以用器件的小信号等效电路模型来仿真整个系统的性能。

运用小信号等效电路模型的另外一个好处是,你可以发现一些对性能比较敏感的电容、电感或者电阻等,如果你能将这些阻容件与器件的物理结构对应起来,那么你就可以对器件进行调优,进而将整个器件的性能调整到最好。

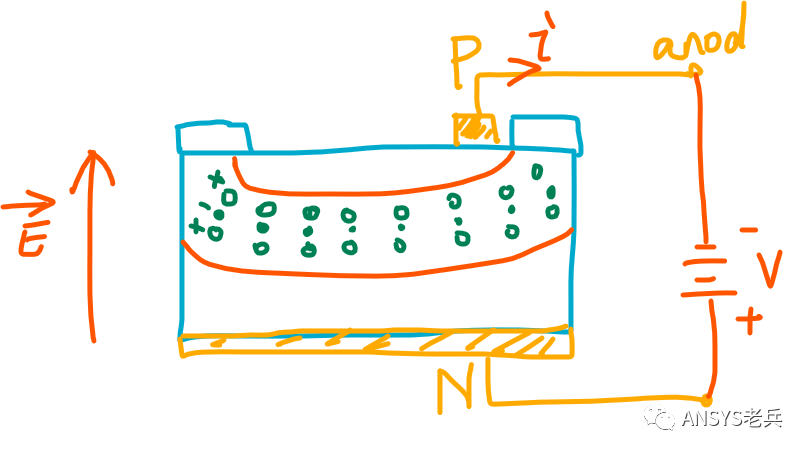

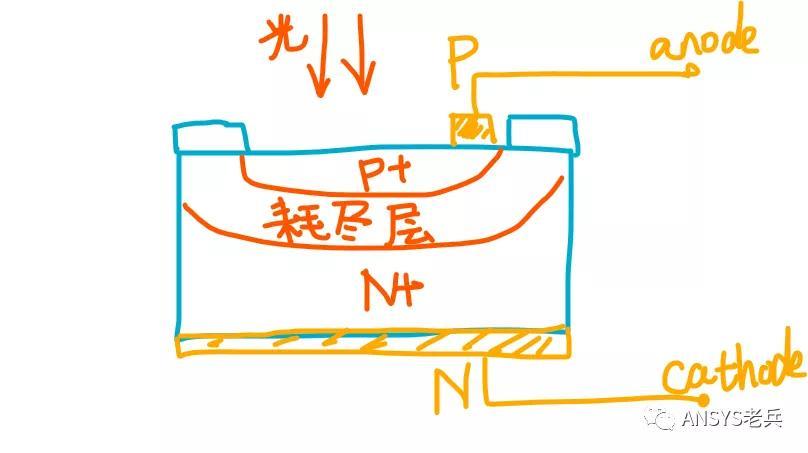

备注:半导体物理我完全是门外汉,一些陈述有错误的话,请大家谅解啊!!(1)、一个简单的P-I-N PD切面图如下,从上到下依次为光敏面、重掺杂的P+、耗尽层、重掺杂的N+衬底,黄色的为top层的anode pad和bottom层的大面积cathode pad,当有光照射的时候,在耗尽区会产生电子和空穴。(2)、在给PD加上反偏电压后,就建立一个从N到P的电场E,高中物理就学过,正电子(空穴)会顺着电场方向移动,而负电子会逆着电场方向移动,而电流的方向又定义为正电子移动方向,因此从PD的正极anode会有电流输出,输出电流的大小跟光功率和PD的响应度有呈正比例关系,参考下面粗糙的图

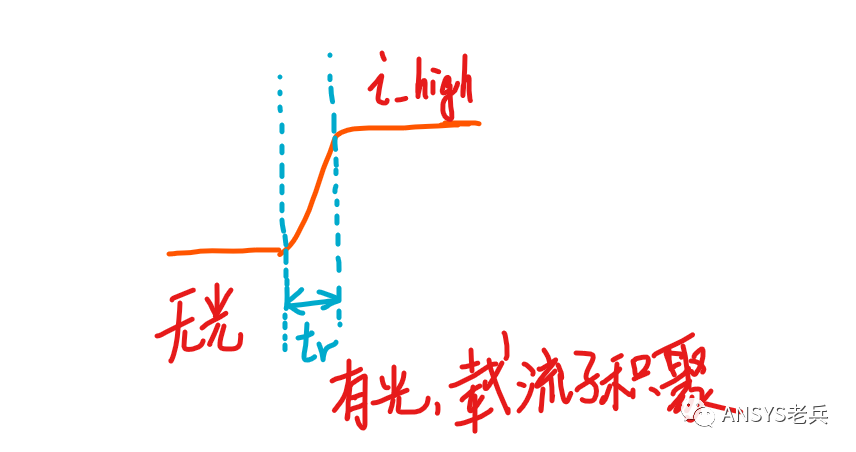

。(3)、根据第二条的陈述,在反偏电压下,从PD的anode端有电流输出,但是这个电流的输出其实是有一个积聚的过程的,既然是积聚,那么就得花点时间。参考下图,当光照射产生电子和空穴时,在整个耗尽层都布满了载流子(电子和空穴),有的载流子离anode pad就远些,有的离得近。离得远,要走到pad的时间就要长点,离得近的就少花点时间,根据公式电流计算公式I=q/t,当电荷q在慢慢增大,电流I也在增大,在经过时间t后,在载流子全部到达pad,电流达到最大,这个时间称之为载流子的渡越时间(transit time)。看起来就是一个rise time和fall time为0的光调制信号,正常也应该是产生rise time和fall time为0的电流信号,但是电流从0到��大有一个积聚过程,也就是rise time和fall time不等于0了,相当于电流经过了一个低通的滤波器,将高频信号过滤掉了,rise time变大了。

。(3)、根据第二条的陈述,在反偏电压下,从PD的anode端有电流输出,但是这个电流的输出其实是有一个积聚的过程的,既然是积聚,那么就得花点时间。参考下图,当光照射产生电子和空穴时,在整个耗尽层都布满了载流子(电子和空穴),有的载流子离anode pad就远些,有的离得近。离得远,要走到pad的时间就要长点,离得近的就少花点时间,根据公式电流计算公式I=q/t,当电荷q在慢慢增大,电流I也在增大,在经过时间t后,在载流子全部到达pad,电流达到最大,这个时间称之为载流子的渡越时间(transit time)。看起来就是一个rise time和fall time为0的光调制信号,正常也应该是产生rise time和fall time为0的电流信号,但是电流从0到��大有一个积聚过程,也就是rise time和fall time不等于0了,相当于电流经过了一个低通的滤波器,将高频信号过滤掉了,rise time变大了。

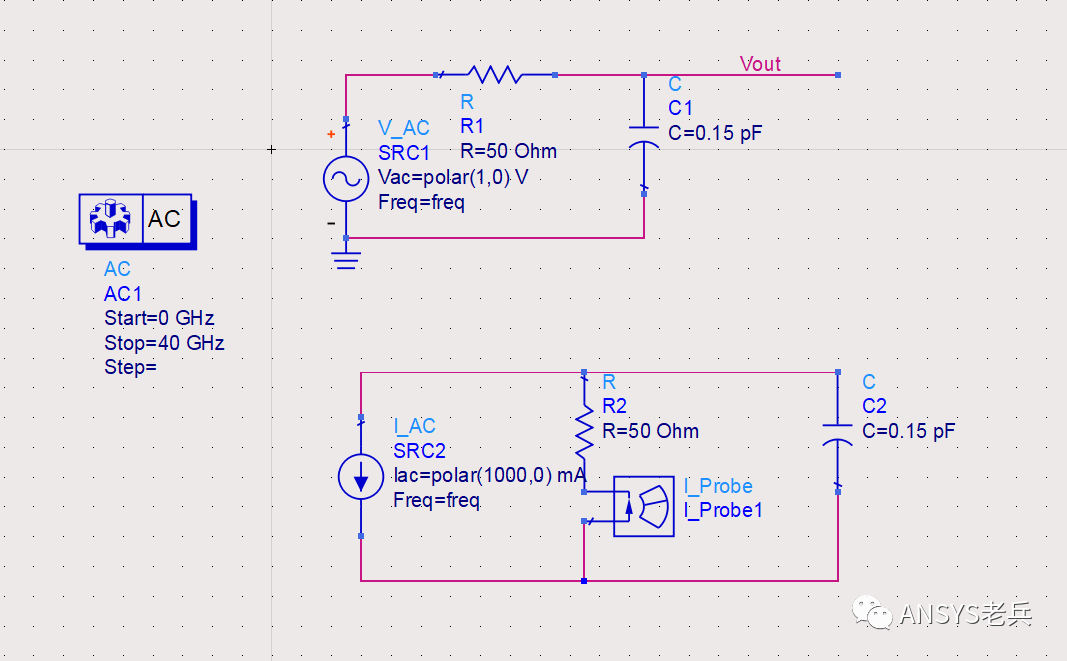

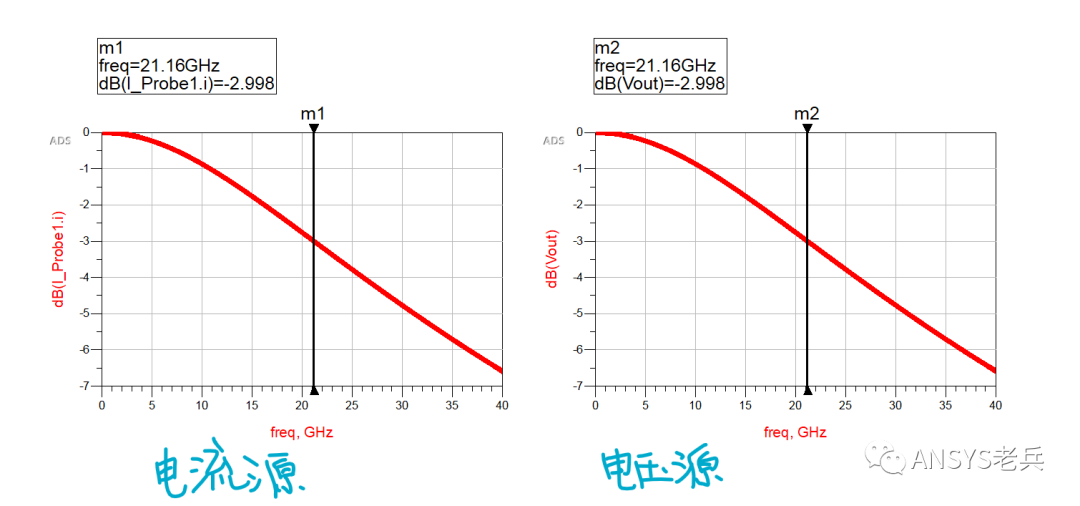

(4)、经常会用一个一阶的RC低通滤波器来产生这个载流子的渡越时间tr,tr=R*C,也就是RC时间常数,同时这个RC也决定了这个低通滤波器的带宽,fc=1/(2*pi*R*C) Hz,在电路上有两种描述,取决于你是用电压源还是电流源,两者的仿真结果是一致的,通过AC simulation得到 R=50ohm,C=0.15pF时,仿真3dB带宽为21.6GHz,理论计算也是21.6GHz,具体如下:

(5)、载流子渡越时间是限制探测器响应度的第一个因素,亦是限制带宽的第一个因素,当载流子流出耗尽区后,还有探测器芯片本身的寄生RLC参数会对带宽产生影响,这些RLC具体有:

- 芯片的结电容,这个好理解,PD反偏,PN几乎全部耗尽,在DC下开路,就相当于放了一个电容在那里,电容的大小跟耗尽层厚度有关系,越厚,电容越小,响应度也会高;

- 芯片串联电阻,载流子在耗尽层产生,要经过重掺杂的P+层,才能到到达P contact(金属),因此这个串联电阻其实是有一定电阻率的P+层表现出来的电阻与P contact的金属电阻之和;

- 芯片串联电感,任意金属都存在电感,其实是p contact这些金属的电感;

- 芯片外围的寄生电容,PD芯片的anode pad和cathode pad之间也是存在电容的,这个电容就是外围的寄生电容,对整个ROSA器件的带宽影响很大,高带宽的PD芯片,这个电容都很小。

在ANSYS circuit电路仿真软件中,自带了一个PIN PD的电路模型,如下图中的各种参数,可以看到,除了考虑芯片的寄生参数外,也要考虑载流子的渡越时间,但是这个模型不太好用,我设置好了参数仿真,经常会报各种error,又没有明确的log提示,help说明也只是简单说明,毫无参考价值,所以此模型建议大家慎用。

(6)、现成的模型不好用,就得捋清楚RLC的具体电路关系,自己搭建电路,这个内容留到这下一篇文章来讲,同时也分析一下PD芯片本身的带宽,以及各寄生参数对带宽和波形、眼图的影响。

注意:关于载流子的渡越时间,我还没找到一些有效的计算公式,或者对应的测试方法,完全依赖于PD芯片厂家提供的数据,有点被动,如果大家知道怎么测试这个时间,欢迎在下方留言。

另外关于载流子的渡越时间的描述也不够全面,更加详细的内容大家可以参考半导体物理的书籍,如果我的这个文章存在错误,也敬请大家指出,谢谢!

。

。