实例探究 | 基于HFSS 3D Layout的时域仿真分析

HFSS 3D Layout是Ansys公司推出的专门用于PCB和封装的全波三维电磁场仿真工具,其计算过程完全基于HFSS的有限元算法内核,同时提供了EDA风格操作界面和仿真设置流程,更加符合layout行业的操作习惯,在确保仿真精度与HFSS一致的同时,很好地弥补了HFSS在PCB与封装仿真中操作便利性上的不足,能够为用户带来良好的仿真体验。

HFSS 3D Layout的内核虽然为频域算法,但其界面集成了时域求解器,故可仅利用HFSS 3D Layout进行时域分析,而无需采用“场路协同”的方式来创建Circuit电路进行仿真,可省去较多的操作步骤,提高仿真效率。

基于HFSS 3D Layout的时域仿真分析

PCB模型

基于HFSS 3D Layout的时域仿真分析

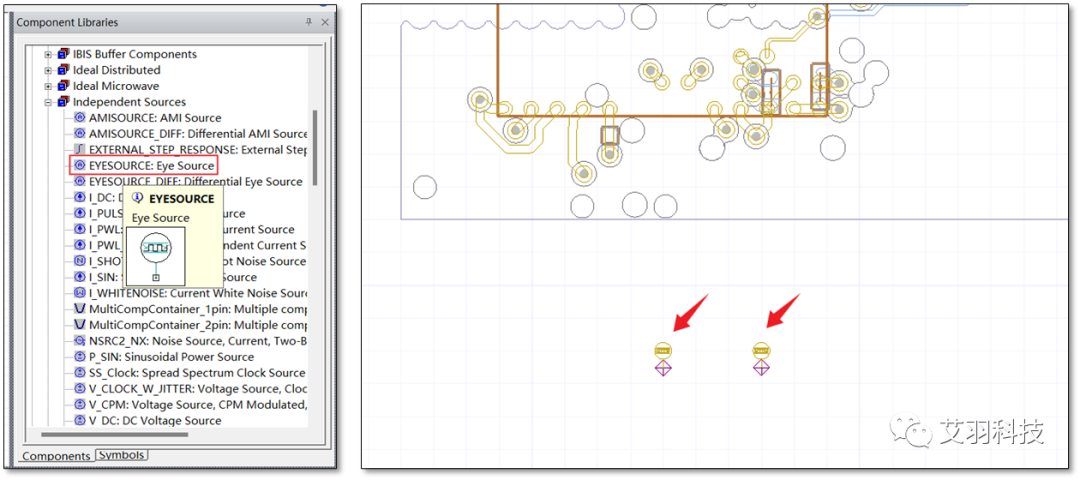

搭建时域电路

基于HFSS 3D Layout的时域仿真分析

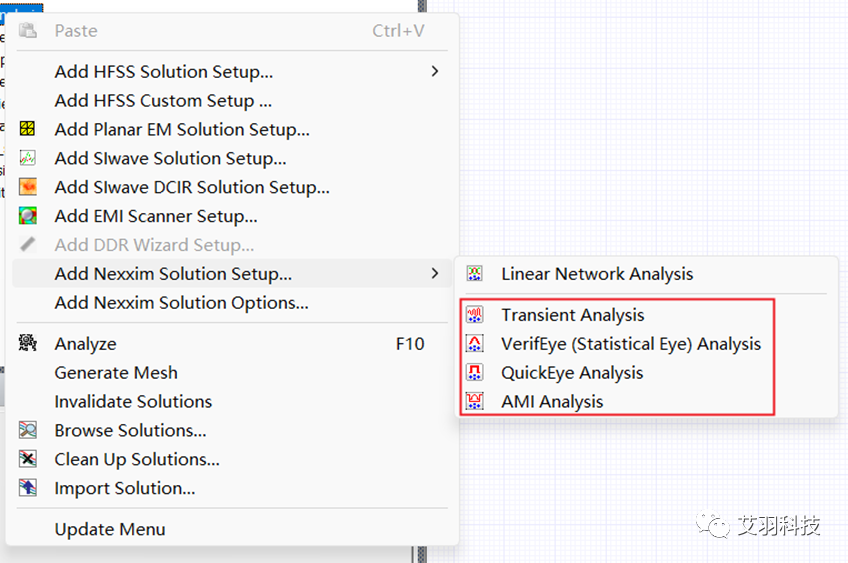

仿真设置

基于HFSS 3D Layout的时域仿真分析

时域结果分析

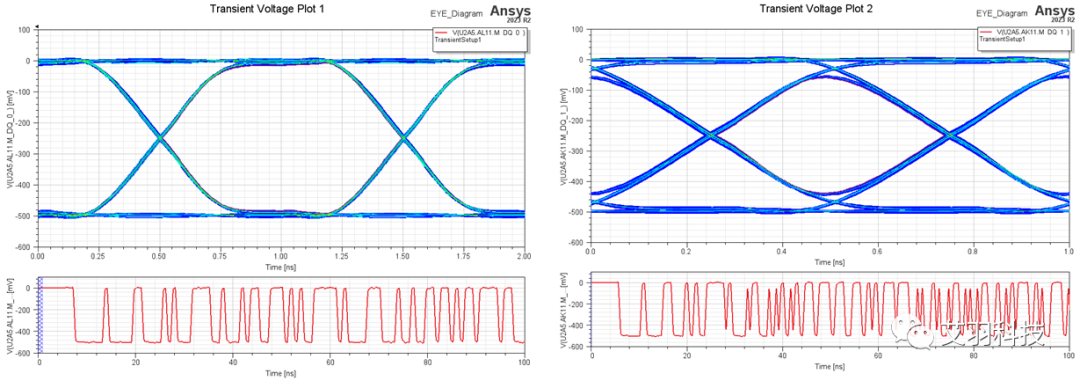

50Ω电阻端接处的时域波形如下图所示,Eye Source不同,得到的时域波形也不同。

两条信号链路上得到的眼图结果如下图所示,不同的信号传输速率,眼图形状不同。

基于HFSS 3D Layout的时域仿真分析

总结

在HFSS 3D Layout中进行的时域仿真分析,实则是本来需要在HFSS和Circuit中进行的“场仿真”和“路仿真”,在HFSS 3D Layout同一设计工程下直接实现了,两种方式可等效,避免了过多的操作步骤,提高了仿真效率。

来源:艾羽科技

登录后免费查看全文

著作权归作者所有,欢迎分享,未经许可,不得转载

首次发布时间:2024-01-02

最近编辑:10月前

还没有评论

相关推荐

最新文章

热门文章