siwave软件对via进行金属化电镀处理的bug问题探讨

本文摘要(由AI生成):

本文介绍了PCB加工中过孔金属化电镀处理的重要性,以及siwave软件在处理过孔时忽略此过程导致的问题。文章指出,siwave在进行电镀处理后会直接导致过孔尺寸变小,进而使via区域的阻抗数值偏大。文章通过实验验证了这一问题,并对比了不同软件间数据传输的差异。最后,作者提醒读者注意siwave叠层、via等参数设置,以避免类似问题的发生。

PCB在进行加工的时候需要对过孔进行金属化电镀的处理,往往在设计的时候,例如孔径为0.2mm的尺寸,板材在加工的时候往往会选择稍微大一点尺寸的钻孔进行钻孔,后期再进行电镀处理来达到与设计的孔径尺寸接近数值,而siwave软件在进行处理的过孔中忽略了这个过程,设置电镀后直接导致该尺寸变小,via区域的阻抗数值比实际的大:

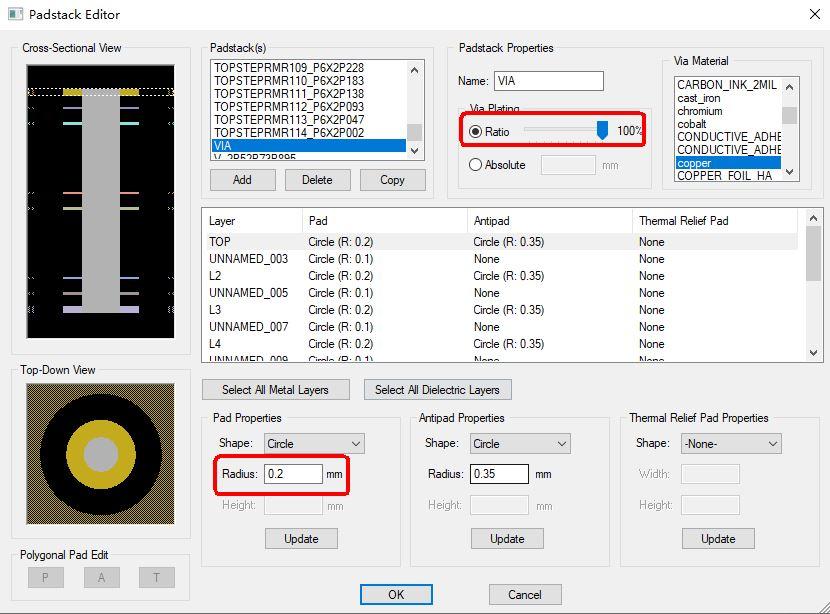

图1:在siwave中查看via的属性

图2:via的参数信息

从图中可以看出via的内径是0.2mm.全部进行的电镀处理,即为实心铜柱

图3:siwave导入到HFSS中的via参数信息(此时全部进行电镀处理),证明导入后信息完整,无丢失

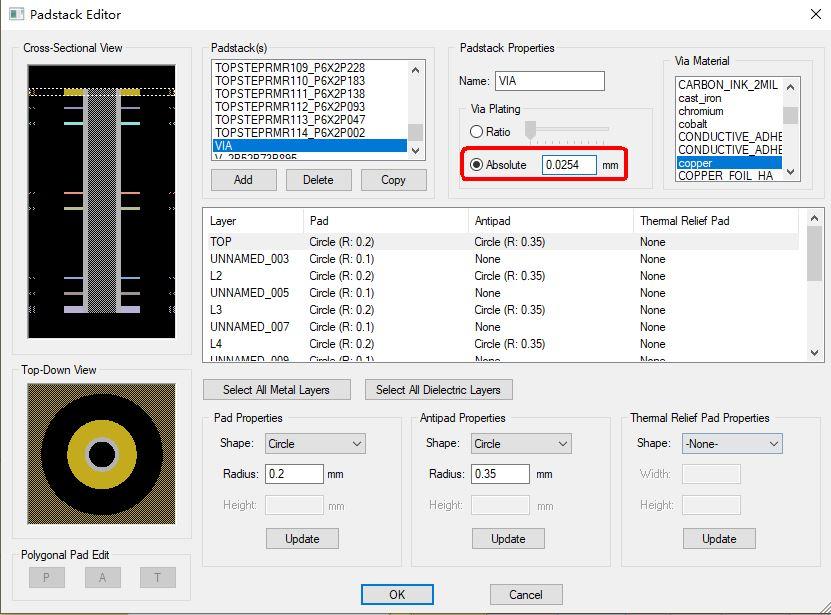

图4:对via进行电镀参数处理:电镀1mil铜厚

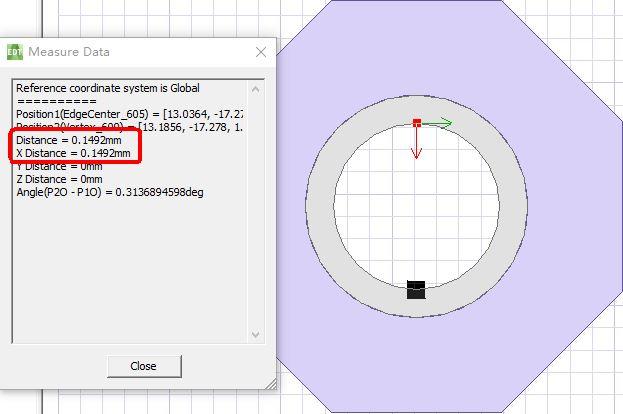

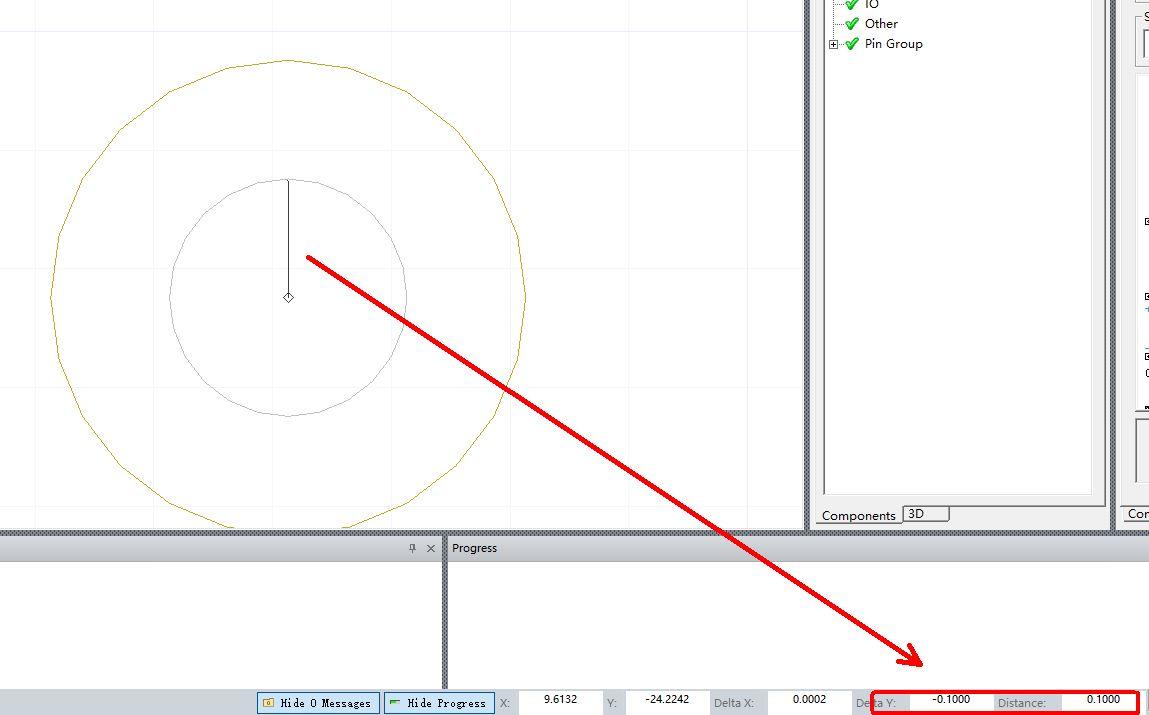

图5:siwave软件导入到HFSS中去进行via内径的测量

此时发现,via的内径尺寸实际是变小了,此时如果将siwave导入的via参数进行直接的仿真,via的阻抗比实际的偏大

那么,siwave导入到HFSS 3D layout中via的参数会不会变化呢,看下图:

图6:siwave导入到3 d layout中数据正常参数一致。

为了再次确认是否3d layout的数值与HFSS是否一致的问题,3d layout导入到HFSS中测量如下;

这时发现,数据一致,没有问题。

总结:siwave via数据导入到HFSS会因为电镀的影响使得内径尺寸变下,而导入到3d layout中并无改变,且从3d layou中传输到HFSS的数据也无此问题。不知道还有那些小伙伴发现了此问题,更详细的解读请参考课程章节:siwave叠层、via等参数设置

课程部分内容截图如下: