Open Drain上下拉电阻计算

集成芯片的数字输出引脚分为开漏(OD, Open Drain)和推挽(Push-Pull)结构。开漏结构可以进行并联实现或逻辑,在后级芯片识别逻辑与本身耐压范围内可以拉到系统的任何电压,使用十分灵活。芯片上常见的OD结构输出常见于DCDC芯片的PG(Power Good)和 LBO (Low Battery),电压监控复位芯片的Reset 和 PFO(Power Fail)等,所有漏开输出都需要使用外部上拉或下拉电阻来保持数字输出处于定义的逻辑状态。

处理OD 输出时,首先需要考虑是需要上拉电阻还是下拉电阻,然后考虑电阻的阻值。

一、计算上拉电阻范围

芯片发出动作信号驱动低输出时则需要上拉电阻。例如TPS62085,具有PG输出,如果芯片的输出电压不处于调节状态,它将驱动低电平。因此,PG需要一个上拉电阻,当芯片允许PG引脚浮动时,它将PG引脚拉高,表明电源良好,使能下级芯片,保证系统正常运行。

*附 TPS62085数据手册PG相关数据。

1.当电源良好,Q1处于关闭状态时,设计 Rpull-up 最大值:

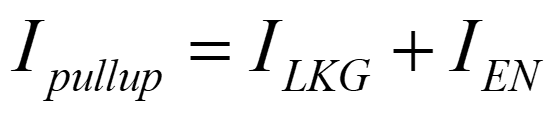

典型PG输出电路(PG浮高)

当Q1关闭,ILKG与IEN 在上拉电阻上产生压降,因此到EN上电压会有降低,为了满足下级芯片EN逻辑高电平。

如果选择更大的电阻会导致RPull-up上的电压降更大,这将导致VPG低于VIH的最小值。后级芯片无法识别PG电压为逻辑高。

2.同样的,当Q1打开,设计 Rpull-up 最小值:

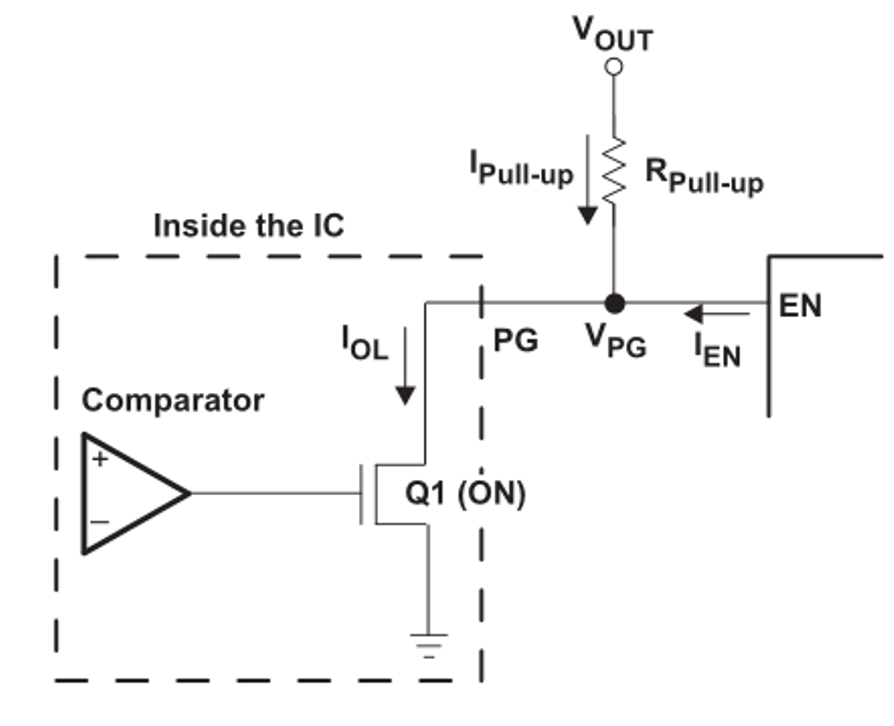

典型PG输出电路(PG低电平)

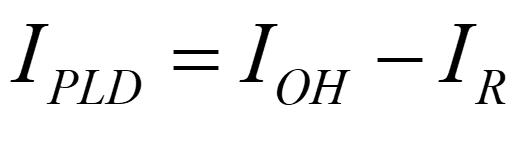

Q1开通导通电阻Rdson使得PG电压高于0V。当Q1接通时,PG电压必须足够低,以shutdown后级芯片。IOL在数据手册作为PG输出低电平 VOL的测试电流。VOL在IOL下不会超过其规定的最大电压。可以使用达到指定的绝对最大PG吸收电流的电流,但它们可能产生高于其指定最大值的VOL。IC的测试电流和后级EN输入的漏电流相减为流过上拉电阻的电流。

上拉电阻两端的电压等于Vout减去VPG。VPG此时的最大值VOL=0.4V。电阻的最小值需要保证Q1中流过电流小于IOL。大于IOL会导致Q1压降无法保证低于0.4V。为了确保符合测试条件,保证VOL最大不超过0.4V,可通过下式计算出最小上拉阻力。

二、计算下拉电阻范围

同理去分析即可得到电阻范围。

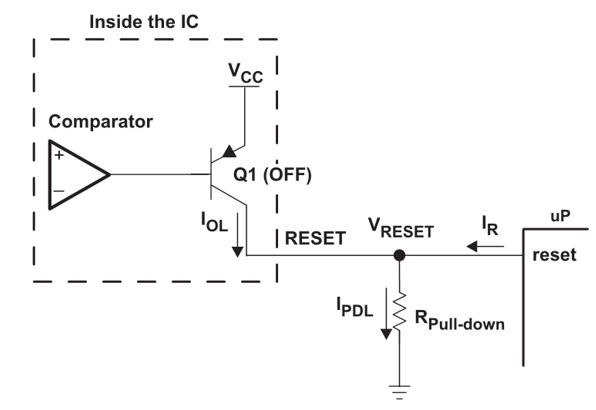

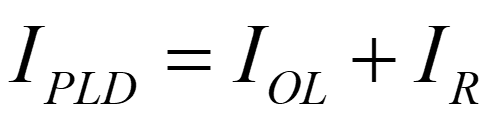

1.当输出不动作,Q1处于关闭状态时,设计 Rpull-down 最大值:

Reset输出等效电路(Reset浮低)

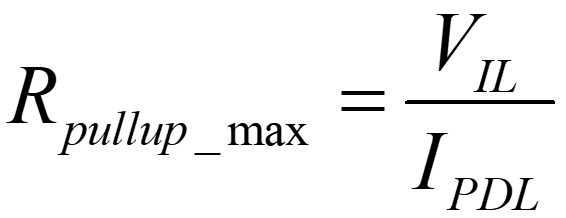

2.当Q1打开,设计Rpull-down 最小值:

Reset输出等效电路(Reset高电平)

实际数据手册会给出建议上拉/下拉的电阻阻值,而且一般电阻可选范围较宽(1k~500kΩ),使用建议值是最方便可以保证系统正常工作。