STA | 2. 绕线延时占比到底有多高?

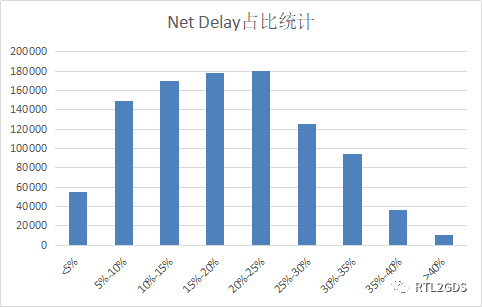

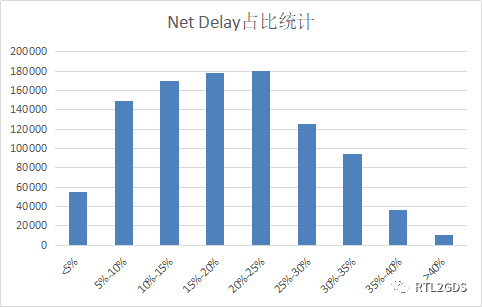

上一篇《STA-1. 从一个反相器开始说时序》中解释了STA中Cell Delay是从标准单元库中得来,那么绕线延时(Net Delay)是怎么计算出来的呢?Net Delay在整个路径延时(Path Delay)的占比又是什么情况呢?针对关键路径,工具会如何降低Net Delay呢?下面我们就来逐步阐述。Path Delay = Cell Delay + Net Delay你可能好奇Net Delay所占的比重如何?这个跟工艺和设计是相关的,但是总体上的趋势是,随着工艺尺寸缩小,Net Delay占比越来越高。下面是Net Delay占比的分布图,统计对象是基于12nm工艺的一个SoC设计中的100万条路径。可以看出,很大一部分的Path中的Net Delay占比超过20%。为了计算Net Delay,我们需要先提取出电容和电阻,如果已经有真实的绕线(route)或者预估的绕线(global route),那么只需要根据route在不同层(layer)的分布就可以提取出相对准确的寄生参数值,下图是在log中显示每一层的layer的单位电阻和电容值的实例,这些值的源头是Foundary提供TLUPlus/ITF文件(本文以ICC为例,其他EDA工具会有较大差异,具体在PnR教程中会讲解):

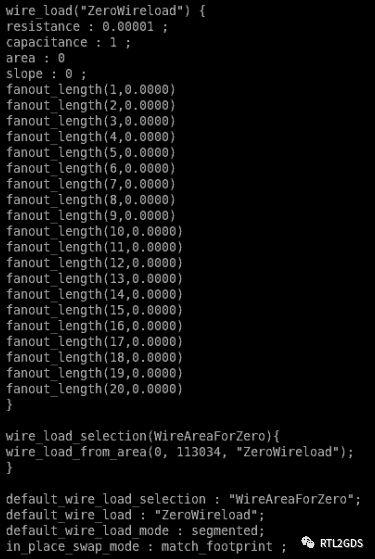

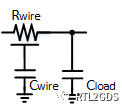

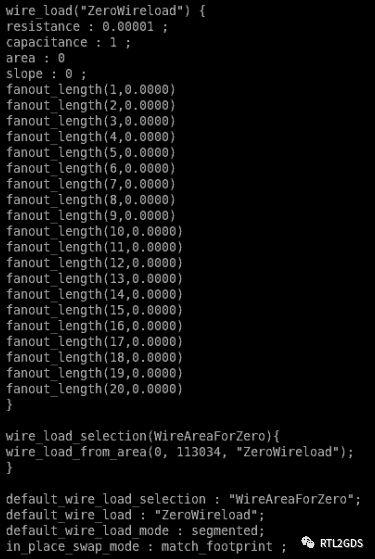

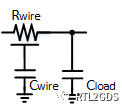

但是,问题来了,在综合(Synthesis)阶段,如果没有绕线的长度信息,也没有stdcell的位置信息,是怎么得到电阻电容值的呢?这就是Wire Load Model在起作用了。下图是标准单元库.lib中定义的一种Wire Load Model,名字是“ZeroWireload”,它是根据net的扇出(fanout)来预估长度(length),然后再根据所定义的单位长度的电阻(0.00001),以及单位长度电容(1)来计算net的寄生RC参数。不过图中的例子比较理想化,都是设成了0,完全不考虑net delay。在实际项目中,必要时,可以自己定义Wire Load Model,尽量在综合阶段将Net Delay的影响考虑进去。既然已经有了寄生的RC信息,那怎么计算Net Delay呢?对于单输入单输出的net,假设不考虑net之间的耦合电容(即不考虑噪声的影响),并且也不存在电阻性的反馈回路的情况,可以用Elmore Delay模型来计算Net Delay,如下图:

根据Elmore Delay公式,各节点的delay可以表示为:

原因是Cwire只能往前看到Rwire/2的电阻,Cload往前能看到Rwire的电阻。

AWE(Asymptotic Waveform Evaluation)和Arnoldi都是是更高级的对RLC网络延时进行瞬态响应匹配近似的方法。当然,AWE本身也有一阶模型,结果与Elmore类似,但是误差也较大(与SPICE模型相比),可能达到74%,二阶AWE模型的误差可以减少到22%,四阶AWE的近似结果和SPICE模型的结果误差已经很小了。AWE模型的优点是容易实现,缺点是数值不稳定,而Arnoldi模型会更加稳健,在目前EDA工具Postroute阶段应用比较多。如果你还有好奇心和多余时间,可以搜一搜这两篇论文进一步了解AWE和Arnoldi模型:《Asymptotic waveform evaluation for timing analysis》和《Reduced-Order Modeling Techniques Based on Krylov Subspaces and Their Use in Circuit Simulation》。

前面讲到Net Delay占整个Path的比重很大一部分已经超过20%了,如何去优化这一部分Net Delay呢?根据Net Delay的计算公式,减少R*C的值就能优化Net Delay。由于高层金属通常会比底层金属的单位长度RC更小,所以把路径上的net更多地绕在高层金属上,可以把关键路径优化得更好。具体到PnR工具的实现上,通常会有一个“Layer Promotion”的功能。另外,对于高速的net,尤其是clock net,一般会特殊对待,给它们设置NDR(Non-Default-Rule),让它们用更大的宽度(width)和间距(space),甚至加上shielding隔离它们,以保证这些高速的net不会被其它的net影响。当然设置NDR是有代价的,它们会占用更多的绕线资源,并不是越严格越好,常见的设置是,对clock net设置2倍宽度2倍间距(2w2s)的NDR。其实高速的net用更宽的rule还有一个DFM的原因,就是这些net的电子迁移(Electro-Migration,EM)导致的绕线缺陷机率比普通net要高。在PnR教程中会详细介绍EM,以及如何避免、修复EM的违例的问题。

对于Net Delay,需要了解它在整个Path Delay占的份量,熟悉Wire Load Model,Elmore Delay,AWE,Arnoldi等概念。有些在后端的面试中也经常被问到。 著作权归作者所有,欢迎分享,未经许可,不得转载

首次发布时间:2023-09-07

最近编辑:1年前