监控用电力仪表的电磁兼容设计与解决手段

1 前言

电力行业常用的监控仪表与传统的电参量变送器相比,逐步向智能化、集成化、多功能化方向发展,并且在电磁兼容性能上也有很高的要求(EMS和EMI试验均有相关要求)。设计者如何选择适当的EMC设计方案,对产品设计的成败起到决定性作用。本文就如何进行电力监控仪表的电磁兼容设计进行了综合阐述。

2 标准解读

2.1 判定标准

结合重工业产品通用标准,电力监控用电力仪表需要满足的EMS、EMI项目及评判等级见图1.

2.2 标准解读

干扰通常分为持续干扰和瞬态干扰两类。如广播电台、手机信号、步话机等属于持续干扰。由于开关切换,电机制动等造成电网的波动,此类干扰我们称为瞬态干扰。图1中瞬态干扰包含:浪涌SURGE,静电ESD,电快速脉冲群EFT/B,电压暂降、短时中断和电压变化DIPS;持续干扰包含:传导敏感度CS,辐射敏感度RS。

评判等级A所述的“性能不降低”,即干扰施加后,硬件无损害,干扰施加过程中无死机、复位、数据掉帧或误码率较高等问题,好像无干扰施加到产品一样。通常持续性的干扰的评判等级均采用此评判等级。瞬态干扰为偶然性发生,且引起的电网干扰时间不长,故暂时性能降低,也就是评判等级B.

2.3 EMS试验项目及干扰实质分析

(1)浪涌SURGE:波形1.2/50μs、8/20μs,是一种脉冲宽度为几十个μs的脉冲,是一种传导性干扰,因其脉冲携带较强能量,故需要对所有功能端口做相应程度的防护,否则会引起内部电路元件的永久性硬损伤。

(2)静电ESD:波形上升沿为0.7-1ns,是一种脉冲宽度为几十个ns的脉冲,因其峰值电压范围在数千至上万伏,故脉冲也具有一定的能量,须在端口做防护。由于其上升沿很陡,故其携带的高频谐波很丰富,可达500MHz,所以静电在仪表所有裸 露的金属部件(包含端子,螺钉等)进行接触放电或孔缝(包含LED指示灯的开孔,各种散热和观察孔)时,或分别对水平耦合板和垂直耦合板间接放电时,均会在放电点瞬时形成一个高频电场,通过空间对电路进行干扰,这种干扰是共模干扰。因此,静电设计时应注意端口保护和空间高频辐射场两方面内容。

(3)电快速脉冲群EFT/B:波形上升沿为5ns,波形为数个周期脉冲串的组合,能量很低。干扰的性质和静电一样是共模,干扰路径既包括传导也包含辐射。

(4)传导敏感度CS:共模干扰,干扰频段从150KHz到80MHz。在进行项目试验时,其干扰信号源至仪表的线缆长度与干扰频段(30MHz)对应的波长λ的1/4比拟,故在施加干扰电压的调制频率超过30MHz时,因趋肤效应,干扰信号主要以空间辐射方式出现(低于30MHz时,主要还是以传导方式干扰)。

(5)辐射敏感度RS:共模干扰,干扰频段从80MHz到1GHz。需注意,外拖的线缆充当接收天线,干扰为电磁场的远场。

2.4 EMI试验项目及干扰实质分析

EMI试验包含传导发射CE和辐射发射RE。CE考察的频段为150kHz~30MHz,RE考察的频段为30MHz~1GHz,通常按A类设备要求。对电力仪表而言,主要考察其内部电源(通常为开关电源)、晶振(包括有源晶振和无源晶振)等主要骚扰源通过天线(由外拖线缆充当)形成的传导和辐射,在设计时应特别注意对上述骚扰源的处理。

3 电磁兼容设计方法

3.1 电磁兼容设计的基本思路

出现EMC问题,必须有干扰源,耦合路径及敏感设备三要素,缺少任何一个环节,均不能构成EMC问题。因此,针对EMC问题,其设计就是针对三要素中的一个或几个采取技术措施,限制或消除其影响,基本思路可分为“堵”和“疏”两类。“堵”就是通过增加共模滤波器,采用光耦等隔离或线缆套磁环等方式增加共模阻抗Z;“疏”就是通过电容形成高频通路,将共模干扰引入阻抗更低的地(PE)或金属壳。一个EMC设计往往可以通过既“堵”又“疏”的方式,在成本增加不大的情况下,可获得较好的EMC性能。

3.2 EMC解决手段

屏蔽、接地和滤波是EMC解决的三种手段。在下文中将详细说明。

4 原理图级设计

在确定仪表需要满足的电磁兼容项目及试验等级后,在原理图设计时就有必要对相关试验项目进行设计,最大程度降低电磁兼容风险和节省项目开发时间。

4.1 端口设计

仪表的端口包括电源端口及信号端口,在EMC测试项目中针对端口的试验包括浪涌SURGE,静电ESD,电快速脉冲群EFT/B,传导敏感度CS,传导发射CE,电压暂降、短时中断和电压变化DIPS。因此在设计中应遵循先进行浪涌防护后进行隔离/共模滤波的顺序进行。

(1)浪涌防护设计

根据仪表端口的定义,浪涌分为差模浪涌和共模浪涌两种。如信号端口(也包含工作电源端口)的进线和回线间为差模浪涌,电路的进线和回线分别对地(接地端子)为共模浪涌。

抑制浪涌最常用的器件就是浪涌抑制器件,如气体防电管、压敏电阻、TVS。不同的端口根据其功能,选用不同的组合方案进行浪涌的防护。例如,当仪表是三相四线输入,因为电压端口为高阻输入,在浪涌等级要求不太高时,一般无须采用压敏电阻和气体放电管。

(2)共模滤波器的设计

通过在端口附近设计共模滤波器,对共模干扰进行旁路。滤除共模干扰也可采取设计隔离元件等增大共模阻抗的方式或通过电容接地(如果端口设计有接地端子,应满足相应安全要求)的方式来实现。

设计共模滤波器,首先应明确共模干扰的频段,以便选择合适的电感、电容参数。若需要同时抑制低、中、高频的共模干扰,有时可采用低频和高频共模滤波器串联的方式来解决。

仪表电源端口往往采用开关电源,由于开关电源是一个重要的对外干扰源,需要在端口设计EMI滤波器。另外,从EMS角度考虑,由于隔离变压器的输入输出间存在较大的分布电容,高频共模干扰可以毫无衰减地从输入耦合至输出,因此也需要在开关电源前设计滤波器。

电源端口基本滤波电路结构见图2。当无PE时,共模电容省略。共模扼流圈在绕制中会产生1%左右的漏感,可直接利用来进行差模滤波,若要加强差模滤波,则可在扼流圈后增加差模电感设计。需要强调的是,图2所示滤波器在进行PCB布板时,应尽量摆放在靠近于端口的位置,且印制线走线应注意控制环路面积,让滤波器获得最大的插入损耗。

4.2 敏感电路及器件设计

在设计中需要注意对易接收电磁干扰的电磁敏感电路和器件的设计。尽量采用抗扰度高的器件,在功能满足的情况下,尽量降低晶振的频率,尽量选择上升沿较缓的器件。

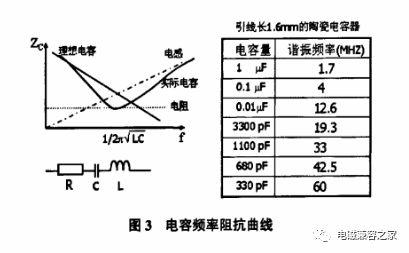

电容、电感非理想器件的寄生参数,在高频时将会大大影响其滤波效果,所以对不同频段的干扰信号应选择不同的滤波参数。以电容为例,其频率阻抗曲线见图3.这里需要强调的是,该类器件的引线过长时,其高频下寄生参数会降低自身的谐振频率,建议尽量采用贴片器件。一个常用的做法是选择参数相差100倍的电容进行并联,以保证在其较宽的频段范围内始终保持电容特性。

数字芯片均应做去耦设计,特别是携带丰富高次谐波的数字电源引脚,通常用0.1μF电容与1nF电容并联。对于数字芯片中因结构、传输路径等客观因素影响的关键信号均应做去耦设计,去耦时应注意不要影响信号的正常传输。

对于特别敏感的电路单元,在成本允许和结构设计时应充分考虑,针对辐射试验项目(RS和RE)屏蔽材料选择铝或铜等金属,设计时为保证足够的屏蔽效能应保证低接地阻抗,在此不作详细说明。

5 结构级、PCB级设计

结构上需要考虑静电放电、射频电磁场辐射、辐射发射三项EMC试验项目,下面主要以因结构限制,在PCB设计中常出现的一些问题进行分析。

常见问题一,仪表因自身结构紧凑,内部常由几块PCB构成,PCB之间通过插针、互联排线等连接,如何进行EMI防护?

这些都是EMC最为脆弱的环节,当连线长度与干扰频率的波长可比拟时,既容易接收到外界的干扰,也容易将内部干扰带出产品,引起EMI超标。

设计时可从以下三方面着手解决:①对插针中传递的信号进行滤波;②尽量减少插针、互联排线的长度(从工艺角度可将其捆扎);③增加地针数目,最好采用“地——信号1——地——信号2——地——信号3——地”方式,减少信号的回路面积,降低不同PCB之间的Zgnd.

常见问题二,针对液晶显示屏,LED指示灯,孔缝等如何进行静电ESD防护?

在设计中建议对液晶显示屏采取透明材料绝缘处理,或增大与内部电路的放电距离。

PCB布线时应注意:①滤波器设计时不要让输入输出分开,避免耦合,最好采用“一”或“L”型;②对关键芯片的敏感信号去耦时,去耦电容应紧靠其管脚,以减小回路面积;③敏感信号不能从晶振底部穿越,也不能离靠近仪表端口,长距离传输时,应注意采用包地方式;④尽量缩短关键信号的传递路径距离,采用伴地设计时,注意增加地过孔的数目;⑤注意不要让敷地存在地割裂情况;⑥通过增加距离来降低相信号通道间的空间耦合;⑦通过正交来解决PCB顶层和底层信号的相互影响;⑧模拟地和数字地在一点处连接,A/D通常视作模拟器件。

常见问题三,如何“接地”?一个产品只有一个接地点。因而,对于接地点位置的选择十分重要,设计时应保证接地点位于干扰信号注入端口且具有低的接地阻抗,通过电容可对共模干扰信号能进行旁路。若仪表端口设计时预留了一个接地端子,可以是前端三相四线输入电压(La、Lb、Lc、N)的保护地PE,也可以是其交流工作电源(L、N)的保护地PE或者还有可能是RS485通讯(A、B)的保护地PE/屏蔽地FG.

地设计时还应保证这个地是干净的地,即EMC中所述的“静地”。当地不干净时,共模干扰信号可能会从地反窜流入信号造成地污染,所以结构设计和PCB设计时,常用做法是在端口预留一块铜箔,让其与内部其它信号分割开来,且留有一定的距离(安全要求考虑)。

6 结束语

电子产品在进行功能设计时,就需要进行电磁兼容方面的考虑,电力监控用电力仪表也不例外。EMC设计需要从原理图、PCB和结构等方面进行综合考虑,并根据实际情况进行相互调整,这样才能最大程度的降低EMC风险,减少EMC整改成本,最终满足相关标准的要求。