【万字长文】 干货|PCB设计经验之谈

布局

一个产品的成功与否,一是要注重内在质量,二是兼顾整体的美观,两者都较完美才能认为该产品是成功的。

在一个PCB板上,元件的布局要求要均衡,疏密有序,不能头重脚轻或一头沉。

印制板尺寸是否与加工图纸尺寸相符?能否符合PCB制造工艺要求?有无定位标记?

元件在二维、三维空间上有无冲突?

元件布局是否疏密有序,排列整齐?是否全部布完?

需经常更换的元件能否方便地更换?插件板插入设备是否方便?

热敏元件与发热元件之间是否有适当的距离?

调整可调元件是否方便?

在需要散热的地方,装了散热器没有?空气流是否通畅?

信号流程是否顺畅且互连最短?

插头、插座等与机械设计是否矛盾?

线路的干扰问题是否有所考虑?

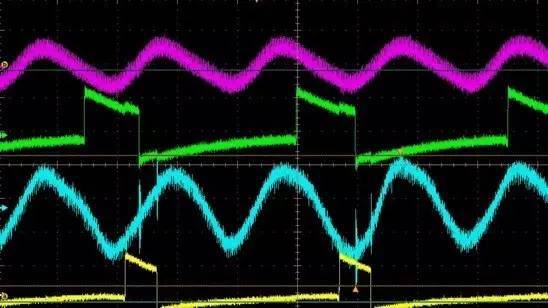

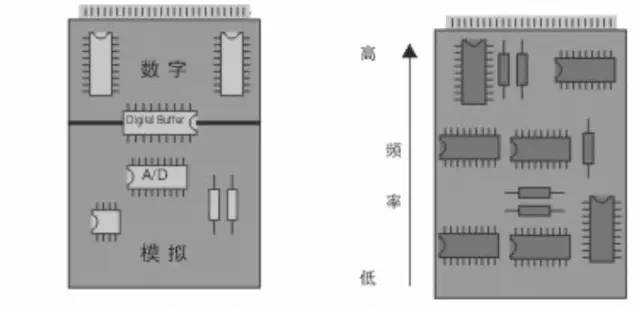

6、数模分离

电路板布线的基本知识既适用于模拟电路,也适用于数字电路。一个基本的经验准则是 使用不间断的地平面,这一基本准则可降低了数字电路中的 dI/dt(电流随时间的变化)效应, 因为 dI/dt 效应会造成地的电势并使噪声进入模拟电路。数字和模拟电路的布线技巧基本相同,但有一点除外。对于模拟电路,还要另外一点 需要注意,就是要将数字信号线和地平面中的回路尽量远离模拟电路。这一点 可以通过如下做法来实现:将模拟地平面单独连接到系统地连接端,或者将模拟电路放置在电路板的最 远端,也就是线路的末端。这样做是为了保持信号路径所受到 的外部干扰最小。对于数字 电路就不需要这样做,数字电路可容忍地平面上的大量噪声,而不会出现问题。

布线

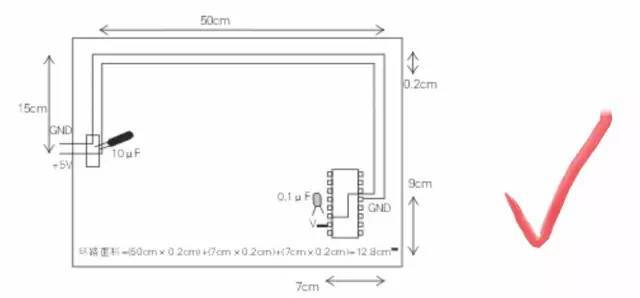

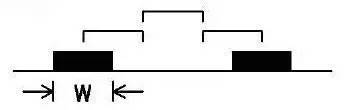

(2)、尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5 mm

对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个地网来使用(模拟电路的地不能这样使用)

(3)、用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。或是做成多层板,电源,地线各占用一层。

2 数字电路与模拟电路的共地处理

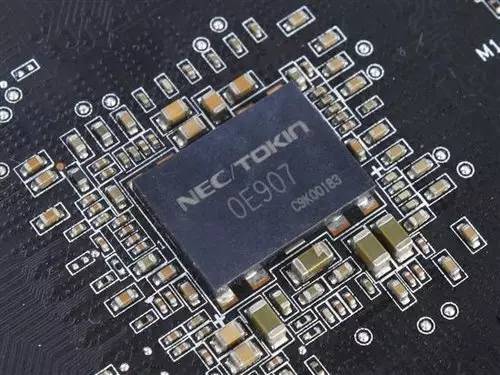

4 大面积导体中连接腿的处理

(2)、电源线和地线的宽度是否合适,电源与地线之间是否紧耦合(低的波阻抗)?在PCB中是否还有能让地线加宽的地方。

(3)、对于关键的信号线是否采取了最佳措施,如长度最短,加保护线,输入线及输出线被明显地分开。

(4)、模拟电路和数字电路部分,是否有各自独立的地线。

(5)后加在PCB中的图形(如图标、注标)是否会造成信号短路。

(6)对一些不理想的线形进行修改。

(7)、在PCB上是否加有工艺线?阻焊是否符合生产工艺的要求,阻焊尺寸是否合适,字符标志是否压在器件焊盘上,以免影响电装质量。

(8)、多层板中的电源地层的外框边缘是否缩小,如电源地层的铜箔露出板外容易造成短路。

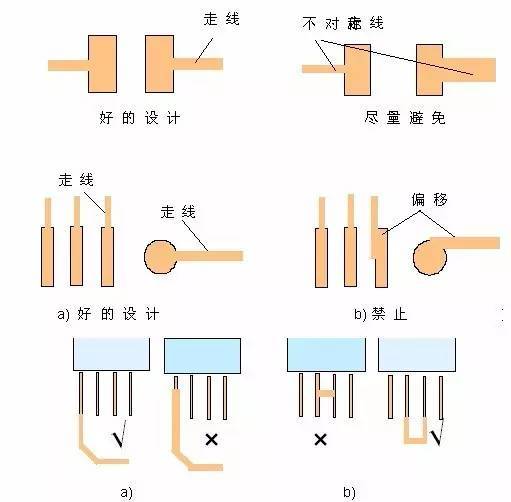

布线约束

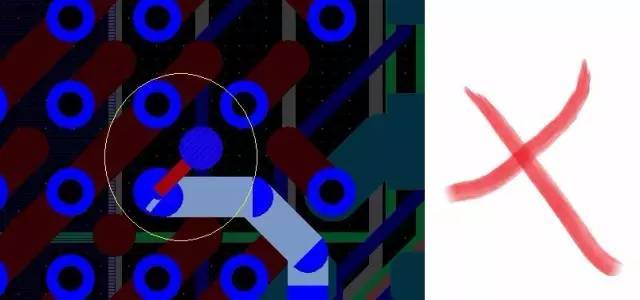

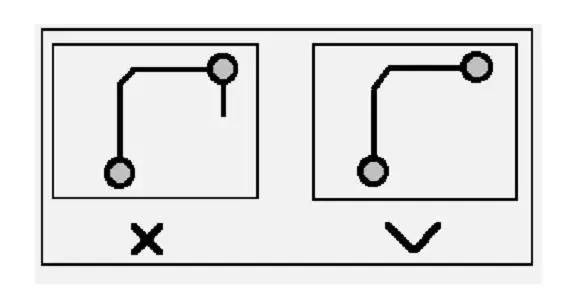

(2)焊盘的出线方式要合理。

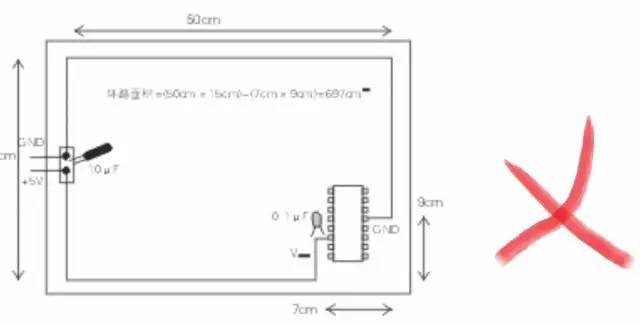

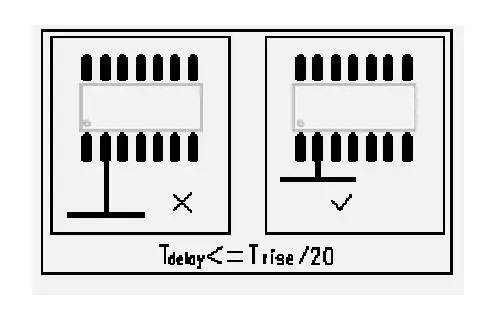

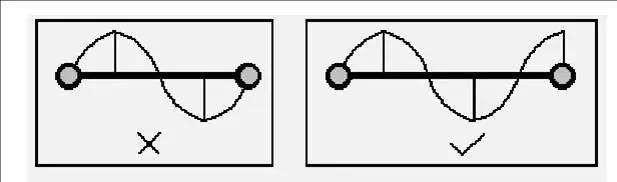

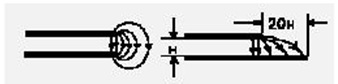

布线基本要求图

电容的接地图

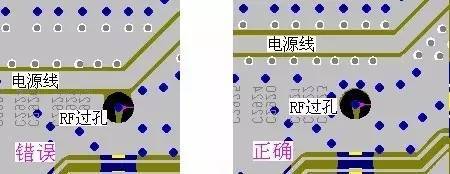

电源线与射频过孔布线图

孤立铜区的出现,将带来一些不可预知的问题,因此将孤立铜区与别的信号相接,有助于改善信号质量

通常是将孤立铜区接地或删除。在实际的制作中,PCB厂家将一些板的空置部分增加了一些铜箔,这主要是为了方便印制板加工,同时对防止印制板翘曲也有一定的作用。

【文章整理】电磁兼容之家

【声明】文章信息来源于互联网,目的在于传递更多信息,不代表本订阅号赞同其观点和对其真实性负责。如转载内容涉及版权等问题,请立即与我们联系,我们将迅速采取适当措施。

登录后免费查看全文

著作权归作者所有,欢迎分享,未经许可,不得转载

首次发布时间:2023-08-10

最近编辑:1年前

还没有评论

相关推荐

最新文章

热门文章