如何在CST仿真中使用多引脚电子元器件

很多CST用户小伙伴在使用CST进行电磁兼容性仿真或者3D电路仿真的时候都会用到很多电子元器件并且要去进行建模,大部分都是可以通过建立离散端口导入元器件Spice或者S参数模型去仿真的,比如电容,电感,Mosfet等等。因为离散端口完美的匹配两端口的电子元器件,对于三个引脚的器件也还比较适用。

但是当我们如果需要用到管脚更多的电子元器件模型,比如运放或者低压DCDC芯片的时候,那么应该如何在3D工作室里面建立模型呢?

今天小编就来分享一下,如何在CST仿真中使用多引脚电子元器件?

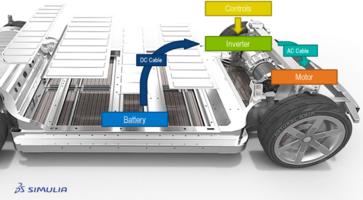

本案例以运算放大器设计的旋变电路为例,很多做高压电驱的小伙伴都知道旋变电路,旋变电路的设计基本有两种电路设计方案。

第一种是二阶有源低通滤波器加单端转差分放大。第二种是二阶有源低通滤波器加晶体管限流放大电路。大多数都是用多端负反馈二阶低通滤波,其他像巴特沃兹二阶低通滤波也可以。

那么我们就来看一下多端负反馈二阶滤波器如何3D建模。电路图大概是这样:

首先导入PCB,这里用的双通道的运放,一共八个管脚,运放八个管脚分布如图

需要仿真计算的电阻电容都用离散端口建立,如图:

从电路上看运放有5个引脚,这里除了GND,还需要四个port,分别是VCC,IN+,IN-,OUT四个pin脚,但是CST没有4端口的离散端口。那么怎么办呢?

首先在这四个pin脚上对地建立离散端口,如图

其中VCC,IN+,IN-这三个pin脚是输入,OUT是输出,需要注意两点:一是需要知道这几个信号激励源在哪,信号是从哪里过来的,显然,VCC肯定从电源端来的,IN+,IN-是从激励信号过来的。二是需要建立输入输出的闭合回路。回路一定要是闭合的。

如图,对地建立输入端的激励信号,激励信号的离散端口和IN-离散端口形成的回路是一个闭合回路,这样激励信号端口的信号才能如图电流路径传导到IN-的离散端口上去,IN+端口因为是参考电压,这边可以直接用电源给个固定的电压值。

同样的运放的VCC来自于低压电源16V,在电源端对地建立离散端口,运放的VCC引脚也是对地建立离散端口,电流路径如图。

输出端口也是用同样的方法建立闭合的回路到下一级放大电路。下一级放大电路也是用同样的方法去添加离散端口才能应用运放spice模型去仿真。

然后我们转到DS工作室,把各个端口连接运放的Spice模型的引脚,把滤波器的电阻电容元器件添加进去。如图:

最后来看一下仿真的结果和实际硬件信号测试的结果

仿真的旋变信号如图,旋变信号的峰峰值11.7V,offset是8V

实测的旋变信号如图,旋变激励信号的峰峰值分别为11.76V和11.68V,offset是8V

.png?imageView2/2/h/336)