遇到一个麻烦事:信号被 干扰了!!!

串扰是信号完整性中的重要内容,影响系统的时序、降低噪声容限,导致系统无法 正常的工作。在电路设计过程中难免遇到信号完整性问题,今天就给大家详解一个关于信号串扰的案例,以前分享过。

1、信号串扰

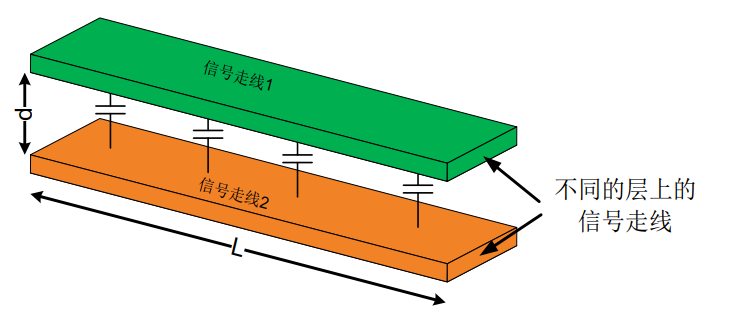

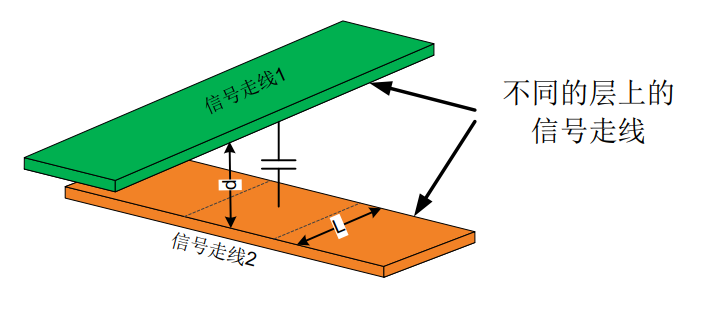

串扰指的是在两条信号线之间的耦合现象。信号因为空间距离近的原因导致的信号线之间会出现不希望看到的电感性和电容性耦合从而互相干扰。电容性耦合会引发耦合电流,而电感性耦合则引发耦合电压。在电路设计中,是一个比较棘手的问题。

平行走线的容性耦合

垂直走线的容性耦合

2、本文概要

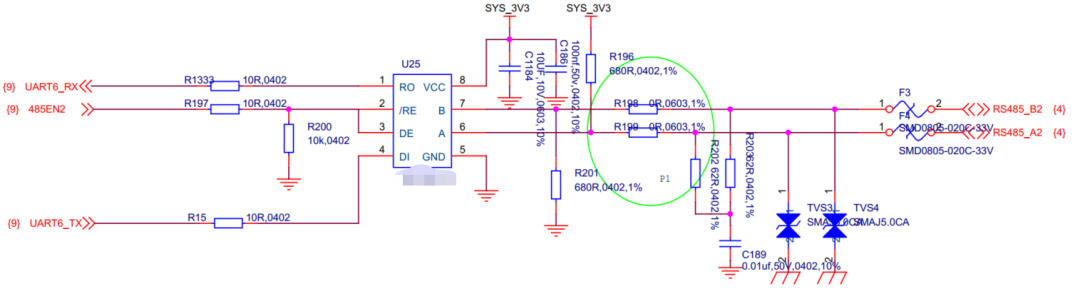

本文要解决的是RS485发送端波形噪声干扰大的问题,如下图1所示是其原理图,RS485的发送,接收,使能控制引脚通过一个10R电阻分别直接连接到MCU端口上。这个电路是目前市面上比较常用的RS485方案,具体的实现方式如下:

在空闲期间,485EN为低电平,MCU处于接收状态;在准备发送数据之前,MCU会先拉高485EN,U25处于发送状态;发送完毕之后,485EN重新处于低电平,U25处于接收状态。此方案的关键是要掌握好控制485EN引脚的高低的时机,否则会有丢包问题。

图 1 RS485 典型应用原理图

3、问题发现及解决过程

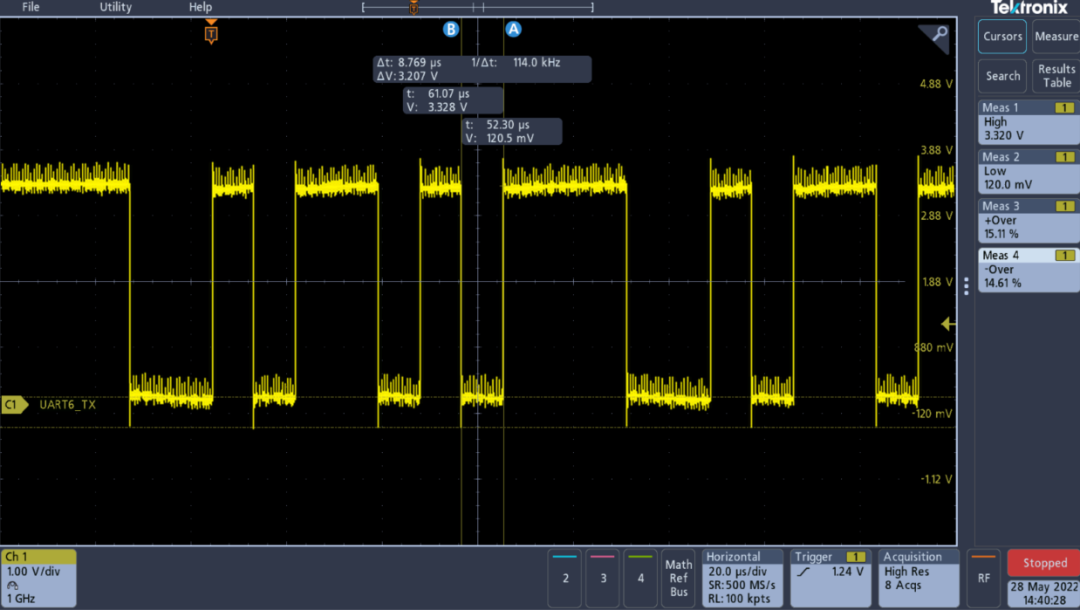

硬件测试时发现发射端DI的波形如下图2所示,在信号上有很大的毛刺(电阻R15前后都一样),测量另外一路同样的RS485电路就不会有这种问题,分析电路原理上是不会有问题的,怀疑是这路信号被其他信号干扰了。

图 2 RS485发射引脚DI(UART6_TX)的波形图

登录后免费查看全文

著作权归作者所有,欢迎分享,未经许可,不得转载

首次发布时间:2023-06-06

最近编辑:1年前

还没有评论

相关推荐

最新文章

热门文章