干货:两级密勒补偿运算放大器设计过程

运算放大器 (简称运放)是许多模拟系统和混合信号系统中的一个完整部分。各种不同复杂程度的运放被用来实现各种功能: 从直流偏置的产生到高速放大或滤波。伴随者每一代 CMOS 工艺,由于电源电压和晶体管沟道长度的减小,为运放的设计不断提出复杂的课题。

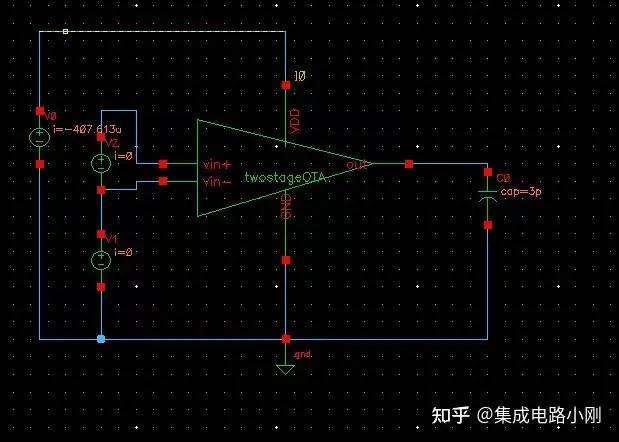

以下内容是小刚设计的一个完整运算放大器,如有错误的地方,大家互相讨论学习,有问题可以在评论区留言。

1)电压

采用smic18mmrf工艺库,其MOS管供电电压为1.8V

2)分配电流

带宽

保证其有60°的相位裕度的情况下,其第二个极点位置为2.2倍的GBW

其中CL为3pf,GBW为100MHz带入其中

由压摆率公式

先取CC=1pf,由压摆率≥ 30 V/us

可求出电流ISS≥30uA

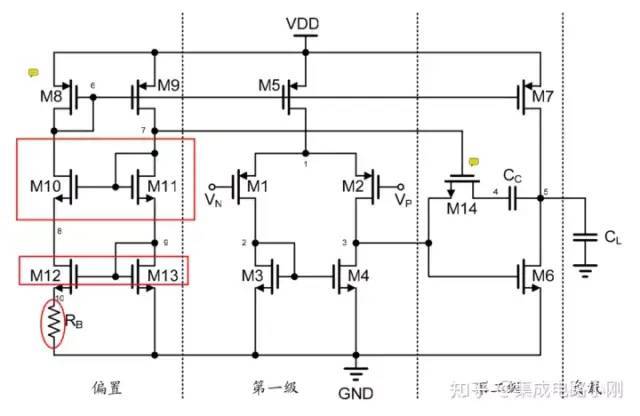

偏置电路

为降低M12的沟道调制效应采用了 Cascode 连接的 M10

以及用与其匹配的二极管连接的 M11 来提供 M10 的偏置电压

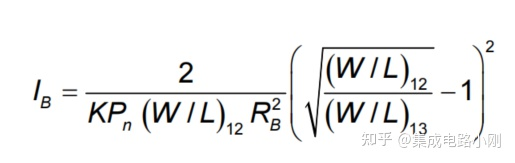

IB仅与电阻 RB和 M12、M13 的尺寸有关,不受电源电压的影响。

取

其总电流是400uA,其中第一级电流为电流源的k1倍第二级为k2倍

设其电流源电流为10uA,

第一级为60uA

第二级为310uA

可求宽长比和RB

(W/L)12=12u (W/L)13=3u RB=7k

先设过驱动电压为100mV求出偏置电流源(W/L)

3)宽长比

电流(ID),尺寸(W/L)和过驱动电压(VGST) 这三个设计参数。根据平方律公式,三个设计参数中只有两个自由参数,由于事先分配好了电流,所以,只要决定了过驱动电压,就可以得到管子的尺寸。所以,如果将所有管子的过驱动电压设为同一值,则各管宽长比的比例可以直接由各管电流之比得到。

在相同电流下,随着 W 的增加,VGST不断减小,扫描图如下:

NMOS

PMOS

所有的过驱动电压设为统一值为150mV

通过比例关系

可求得大部分MOS的宽长比。取MOS管的L为1um,可以求得其W。

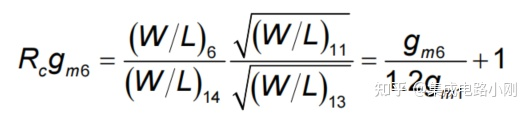

4)相位补偿

由于采用线性 MOS 管和特殊的偏置电路实现补偿电阻,选择让 z1在 1.2GBW 处

大致求出MOS14的宽长比为17/1

当单位增益带宽不够时,根据以上公式

减小CC或者增大第一级电流,通过减小CC的方式发现其相位裕度变化很大,所以通过改变第一级电流的方式,将第一级电流改为100uA其GBW有较为大的改善,同时还可以改善其压摆率指标。从第二个极点位置的角度出发,改变gm6的值的大小,但是发现其GBW变化不明显。

以上为总的分析过程。

1)单位增益带宽和相位裕度仿真

将第一级电流由60uA提升至120uA,GBW上升至100MHz附近,但是相位裕度不够,调节密勒补偿电容至1.5pF相位裕度提升至60dB

但是其带宽下降至79.2MHz

根据公式

所以尝试在保证过驱动电压不变的情况下,提升第二级电流,

由200uA提升至240uA

带宽提升至85MHz,相位裕度63.5°

带宽和相位裕度指标基本满足要求

仿真其余指标(压摆率、噪声、共模抑制比、电源抑制比)

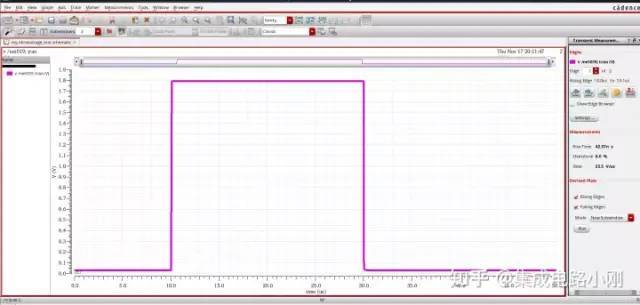

2)压摆率测试

上升沿24V/us,下降沿177V/us

适当降低Cc为1.3pF,相位裕度不够,压摆率提升不明显

决定提升Iss,将第一级电流改成160uA计算得到压摆率一直为25.5V/us不变,改变电流其值大小不变,这是一个疑惑点?

同时上升沿和下降沿的压摆率相差很大。

3)仿真噪声参数

128.042nV/sqrt(Hz)

4)共模抑制比

差模增益86dB

共模增益2dB

共模抑制比84dB

5)电源抑制比

106dB

其最终仿真结果如下(右边为指标要求):

| 静态功耗 | 804uA*1.8v | ≤ 2 mW |

|---|---|---|

| 单位增益带宽 | 92.5MHz | 100MHz |

| 压摆率 | 25.5V/us | ≥ 30 V/us |

| 开环单位增益 | 86.6dB | ≥ 80 dB |

| 相位裕度 | 60.1MHZ | ≥ 60 degree |

| 共模抑制比 | 84dB | ≥ 60 dB |

| 负电源抑制比 | 106dB | ≥ 80 dB |

| 等效输入噪声 | 128.042nV/Hz @1KHz | ≤ 300 nV/ Hz @1KHz |

END

作者 | 小刚

排版 | 黑小姐

图片 | 原创、创客贴

参考资料 | 二级密勒补偿运算放大器设计教程