高速PCB设计:AM335X芯片核心板8层PCB实例详解(附直播)

- 作者优秀

- 优秀教师/意见领袖/博士学历/特邀专家/独家讲师

- 平台推荐

- 内容稀缺

导读:大家好,我是林超文,仿真秀专栏作者,深圳市英达维诺电路科技有限公司总经理,著有《Altium designer实战攻略与高速PCB设计》、《高速高密度PCB设计攻略》等多本PCB工程技术著作,在仿真秀有对应视频教程。擅长高速高密度PCB设计,并高效指导研发人员开展高速PCB设计,提高产品开发效率、提升产品设计质量。通过长期不懈的学习、探索与总结,已初步形成了一套系统化高速PCB设计的实践经验及理论。

一、写在文前

本章采用TI公司的AM335x芯片构建的最小核心板系统,能通过外接DC电源让核心板直接运行,与底板通过B2B连接器连接。底板配合核心板提供了串口、CAN总线接口、USB Host、OTG、LCD外扩、千兆网口外扩等丰富外设,让开发人员能快速整合资源并形成有效的项目解决方案。核心板集成度高、低成本、低功耗、功能齐全,主要特点如下 :

(14)HMI工业人机界面

二、模块PCB设计指南

1、原理框图

单板的信号流向图,即原理框图,如图23-1所示。

图23-1 原理框图

2、单板工艺

单板布线工艺主要取决于单板的高密度芯片的封装工艺(即BGA的间距),以及PCB成本和性能的考虑。推荐的单板工艺设计如下:

(1)单板尺寸:71 x 47 mm。板厚:1.6mm

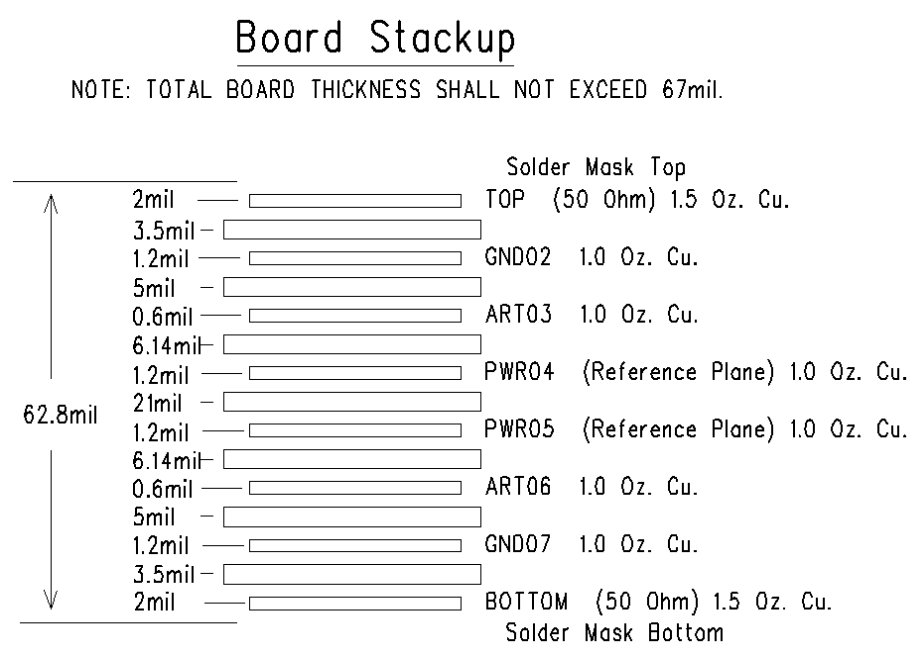

(2)建议采用八层板设计:TOP、GND02、ART03、PWR04、PWR05、ART06、GND07、BOTTOM

(3)过孔规则:孔径8mil/盘径16mil(BGA区域)、孔径10mil/盘径18mil(除BGA的其他区域)

(4)最小线宽规则:5mil(BGA局部区域)

(5)最小线距规则:4mil(BGA局部区域)

3、层叠和布局

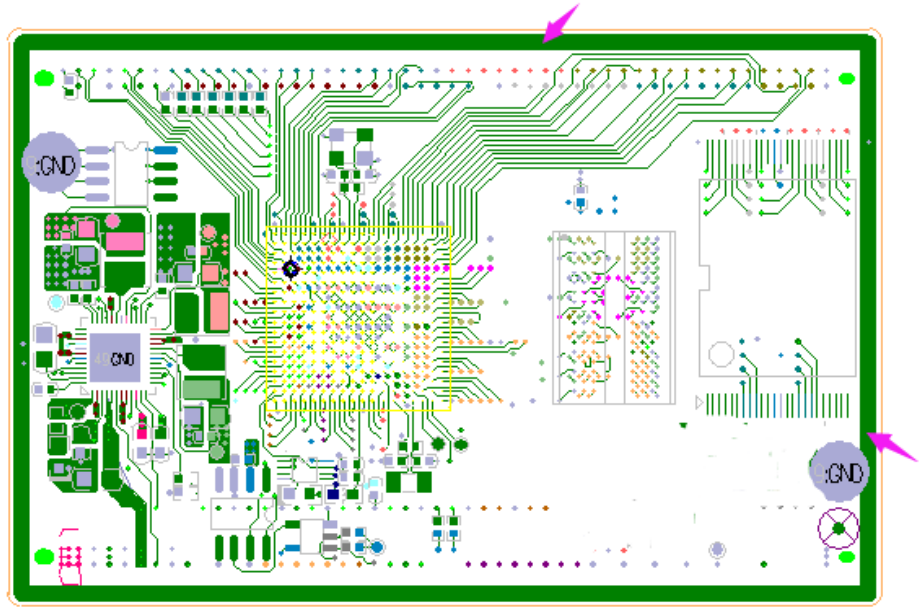

单板采用八层的层叠设计如图23-2所示。

图23-2 八层板层叠设计

单板的布线情况如下:

(1)TOP层作为主要元器件层,主要摆放芯片、钽电容、电感等高度较高的元件;

(2)第3层和第6层相邻层除了地平面,还有两个分割的电源平面,在安排布线时需注意高速信号线的跨岛问题

(3)第2层和第5层作为完整的接地平面,为表层的元器件和布线提供屏蔽和最短电流返回路径的作用

(4)第4层和第5层为主电源平面,为主要电源提供平面分割形式的电源网络

(5)Bottom层放置两个2x50 Pin板对板连接器、BGA和DDR3区域的滤波电容。

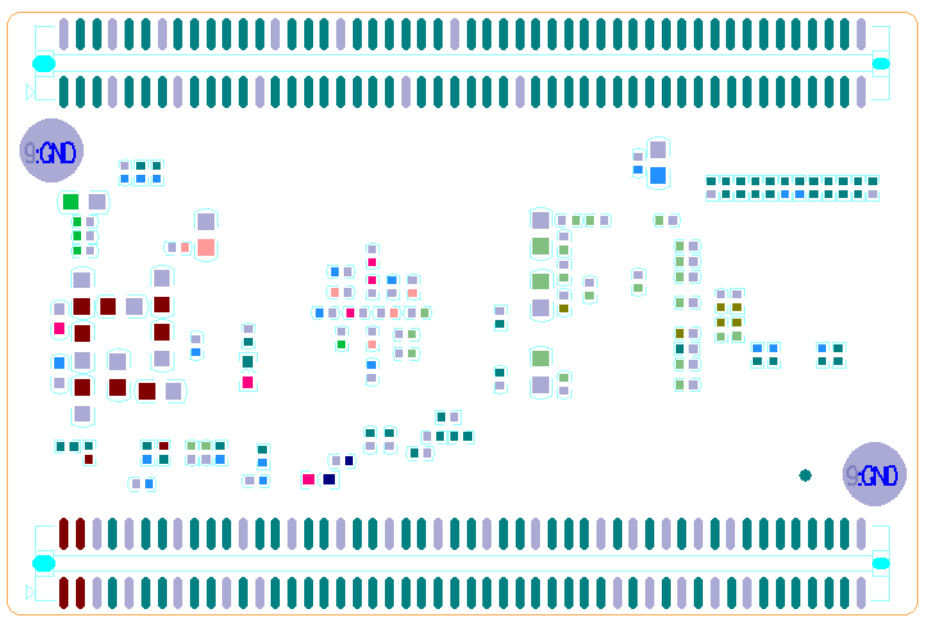

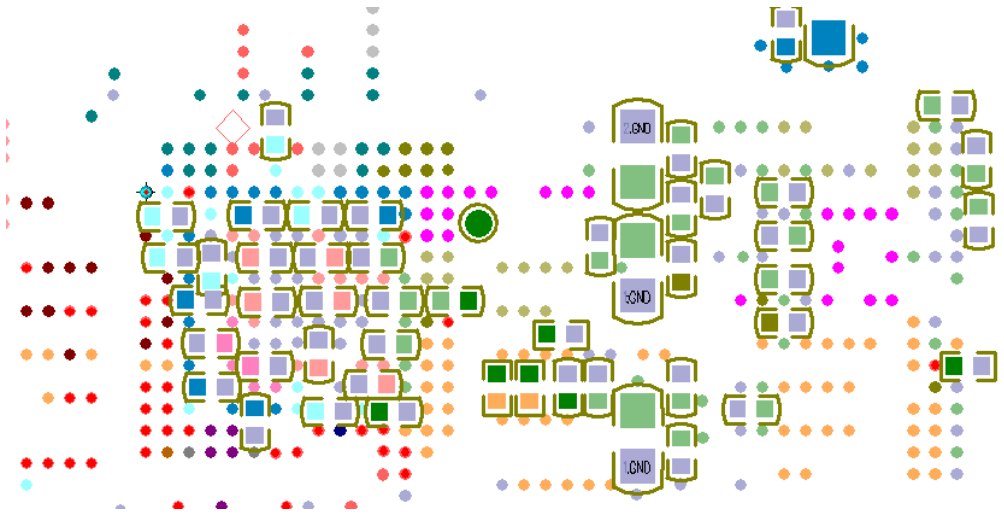

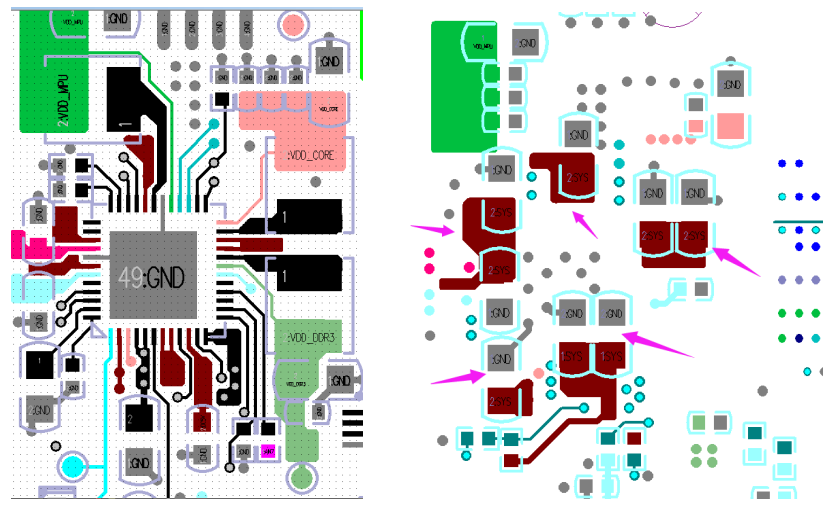

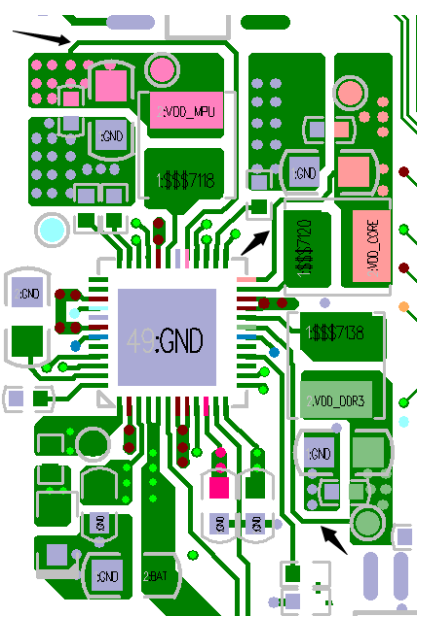

单板TOP层布局规划如图23-3所示。

单板Bottom层布局规划如图23-4所示。

图23-4 分区布局规划

4、屏蔽处理

为了降低EMI及提高产品的可靠性,在TOP层的板边四周用1mm的铜皮进行裸铜开窗。如图23-5所示。

图23-5 屏蔽处理示例

为了能够提供良好的信号回流路径,同时改善铜皮散热的性能,需保证主控和DDR3下方铺铜的完整性及连续性。如图23-6所示。

图23-6 完整平面处理

注意:

(4)过孔与铺铜的安全间距设置为5.5mil。

5、模块PCB设计指南

(一)处理器

AM335x提供高达720MHz的主频速度和支持mDDR/DDR2/DDR3,并配有NEON™ SIMD协处理器、SGX5303D图形引擎。同时AM335x提供了丰富的接口资源。极高的性价比,使得它能适用性极广。

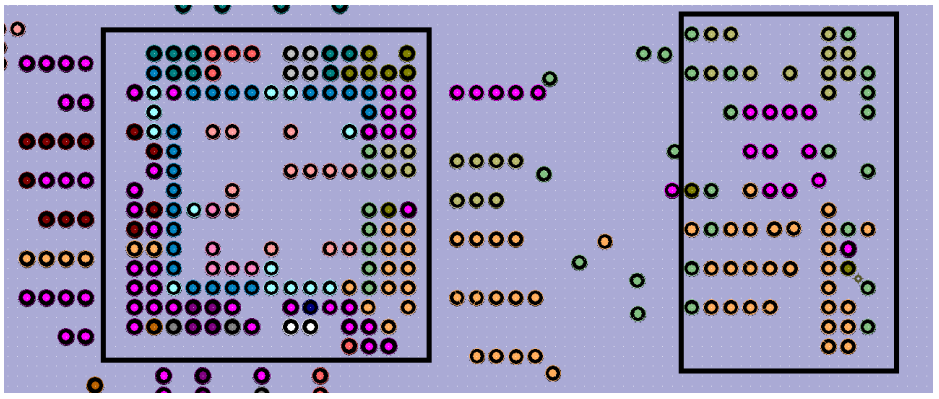

AM335X采用324pin的BGA封装,球距为0.8mm,采用8/16mil的过孔进行Fanout设计,通常将BGA外围前两排焊盘通过走线引出至BGA外部。第三排开始通过过孔就近fanout。AM335X Fanout情况如图23-7所示。

图23-7 AM335X Fanout示意

a、去耦电容处理

芯片的电源管脚需要放置足够的去耦电容,推荐采用0402封装0.1mF的陶瓷电容,其在20~300 MHz 范围非常有效。

去耦电容的处理规则如下:电容尽可能靠近电源管脚。芯片上的电源、地引出线从焊盘引出后就近打VIA接电源、地平面。线宽尽量做到8~12mil(视芯片的焊盘宽度而定,通常要小于焊盘宽度20%或以上)。电容则放置在过孔与过孔之间的间隙。如图23-8所示。

图23-8 去耦电容布局示例

b、晶体处理

晶体谐振器PCB设计要点如下:

(1)时钟电路要尽量靠近相应的IC

(2)晶体谐振器两个信号要适当加宽(通常取10~12mil)

(3)两个电容要靠近晶体放置,并整体靠近相应的IC

(4)为了减小寄生电容,电容的地线扇出线宽要加宽

(5)晶体谐振器底下要铺地铜,并打一些地过孔,充分与地平面相连接,以吸引晶体谐振器幅射的噪声,或者立体包地

图23-9所示是实际使用晶体的PCB布局布线的例子。

图23-9 晶体布局布线示例

(二)SDRAM内存器

本系统采用单颗2Gb容量的DDR3,主电源由PMIC的提供1.5V稳定供电。DDR3相比DDR和DDR2有更快的速度外,另一个区别就是3代的芯片有REST引脚,ZQ引脚。还有则是3代的芯片采用了一些新技术,所以有更快的速度更低的功耗,其供电电压为1.5V。

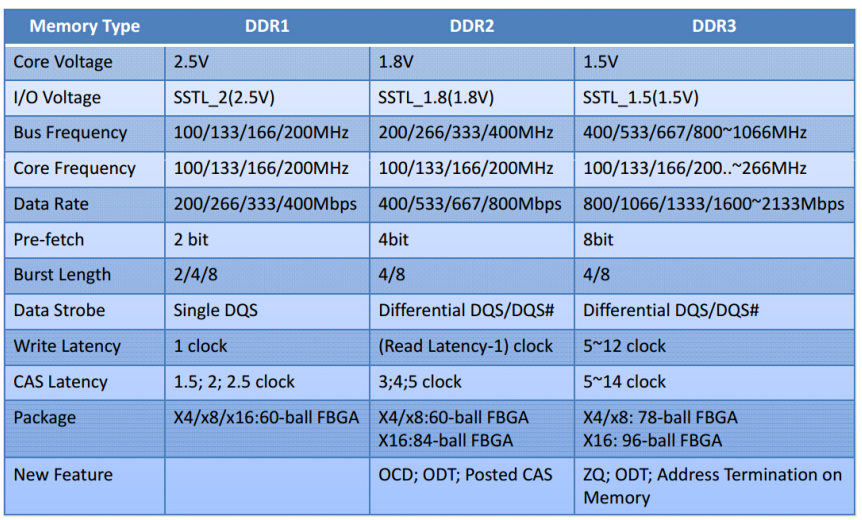

表23-1总结了DDR,DDR2,以及DDR3的一些重要的区别:

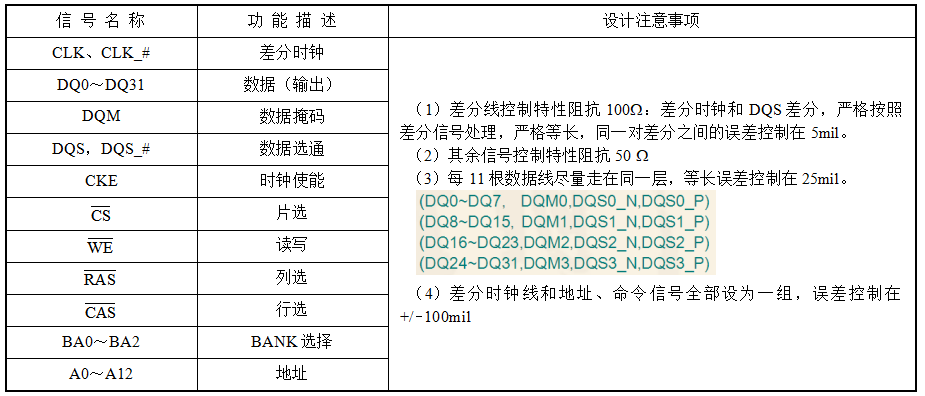

DDR3关键信号处理要点如表23-2所示。

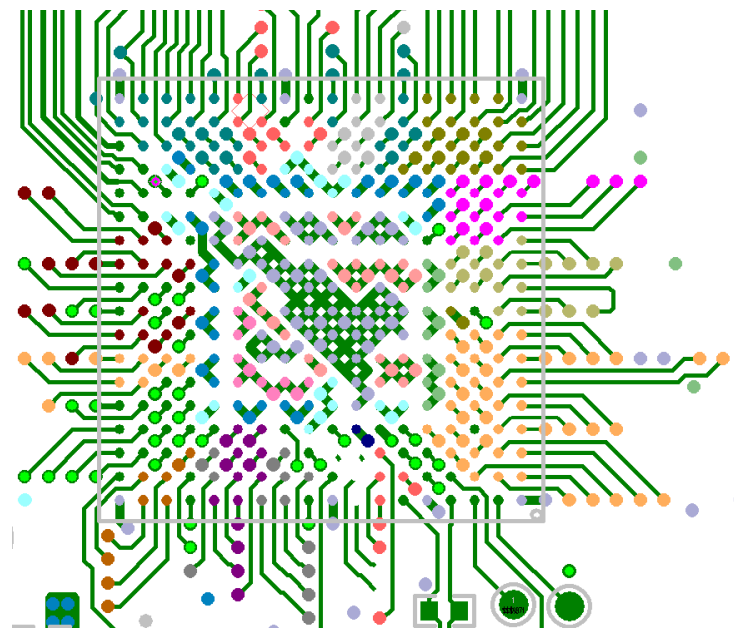

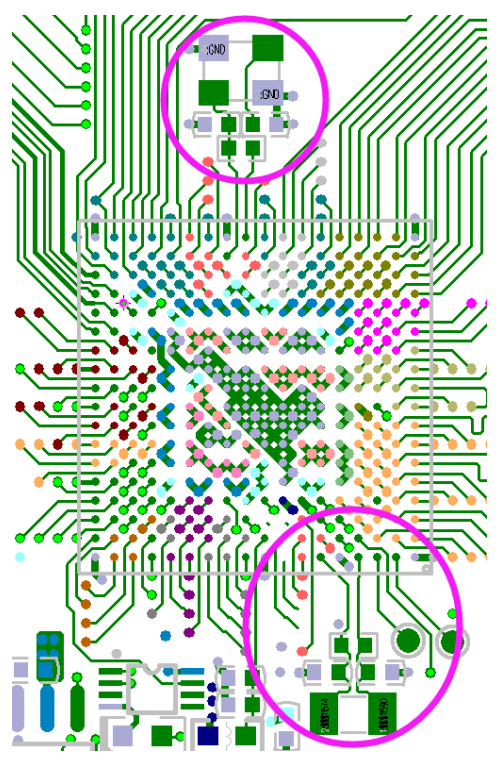

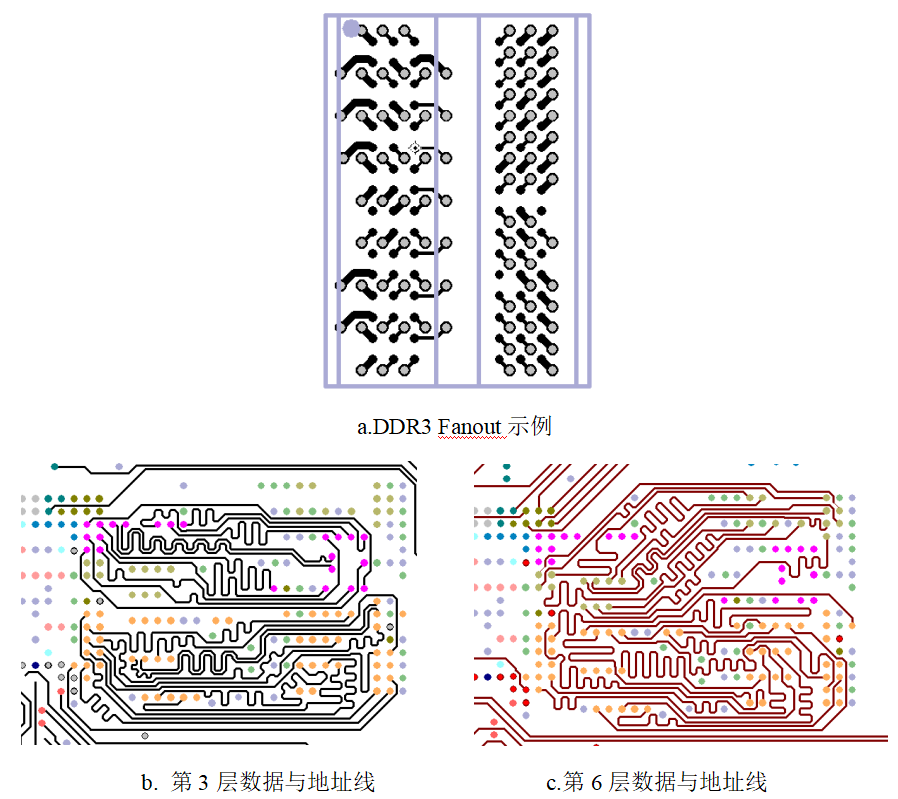

其 Fanout和布线等长情况如图23-10所示。

(三)PMIC

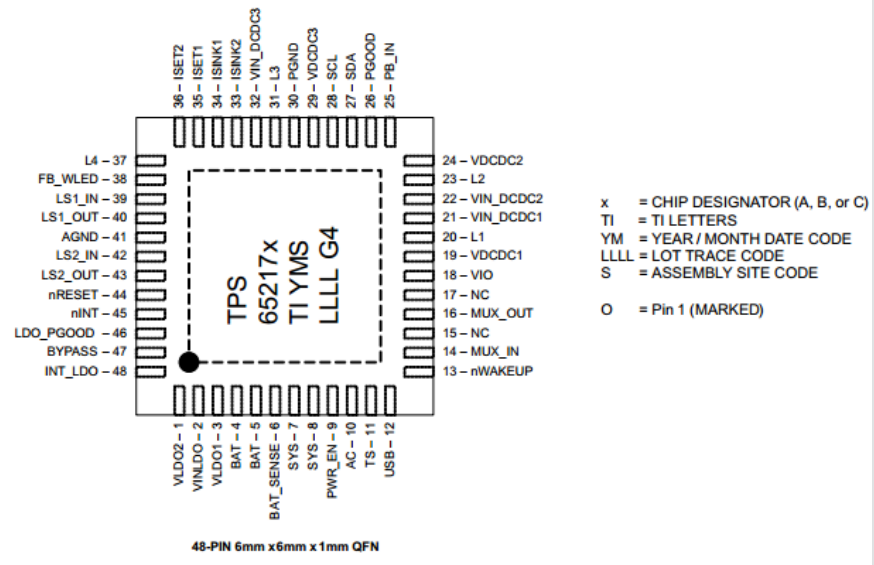

5V电源连接器直接供给AM335x系列配套的电源管理芯片TPS65217C,TPS65217C产生各路电源提供给CPU、DDR等设备。PMIC输出的各路电源通过底板上的LED显示TPS65217C是否工作正常。AM335x通过I2C0来控制TPS65217C。如图23-11为TPS65217C管脚排序。

图23-11 TPS65217C管脚排序

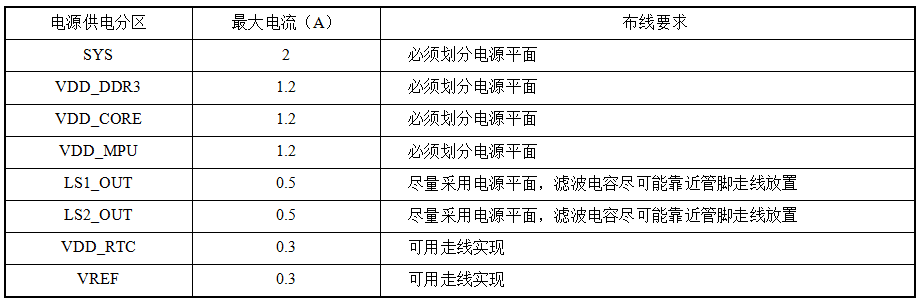

其外部电源供电管脚分配,如表14-3所示。

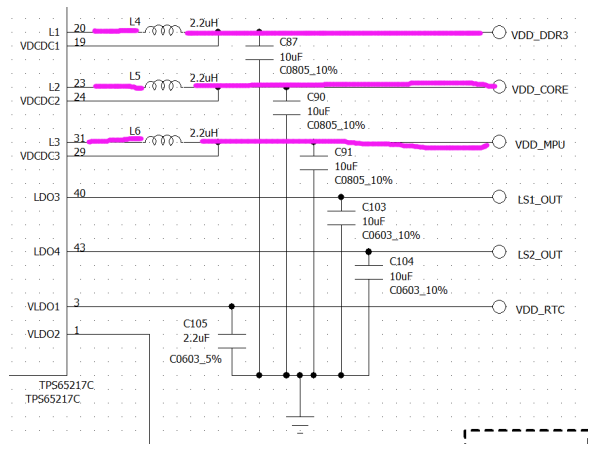

PMIC在布局时要注意预留出芯片电源输出大电感的位置,因为此处是PMIC输出的大电流,大电流示意如图23-12所示。大电感通常放置在Top层,同时需要将PMIC的20,23,31管脚到大电感采用铜皮连接。另外,PMIC输入管脚的滤波电容全部放置在Bottom层靠近输入管脚附近。如图23-13所示。

图23-12 PMIC 大电流示例

图23-13 PMIC 布局布线示例

PMIC的19,24,29管脚为电压采样信号,需要单独接到输出端的末端,即输出滤波电容打孔的位置,如图23-14所示。

图23-14 电压采样走线示例

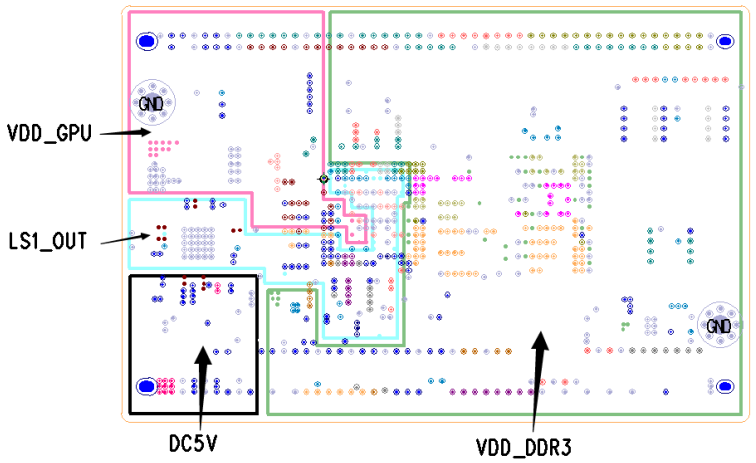

第4层电源平面划分如图23-15所示:

图23-15 第4层电源平面划分

第五层电源平面划分如图23-16所示:

图23-16 第5层电源平面划分

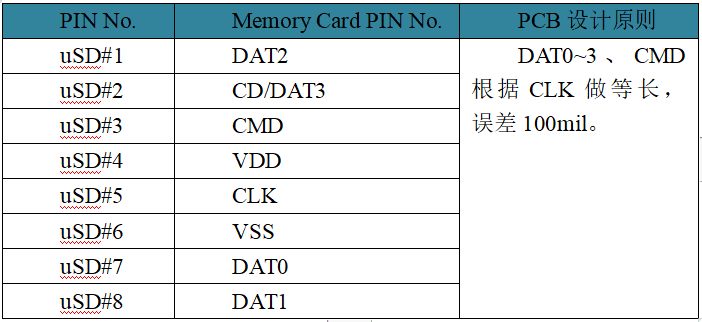

(四)SD/MMC0

AM335x通过MMC0端口连接到Micro SD 卡槽。表14-4为Micro SD 卡槽信号分配表和PCB设计原则。

(五)USB信号

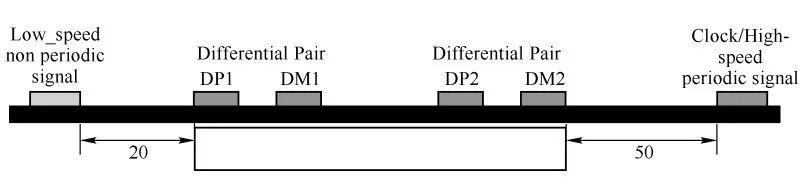

USB设计要点如下:

(1)TVS器件必须靠近插座放置,在PCB设计时要大面积接地

(2)布局保证信号流经TVS后再到共模电源

(3)差分线特性阻抗为90W,等长误差为5mil

(4)两组差分线之间的间距保持4w,并与其他信号或灌铜的间距也要保证4w,如图23-17所示。

图23-17 USB布线间距

(5)优先邻近接地平面走线

USB PCB设计实例如图23-18所示。

图23-18 USB PCB设计实例

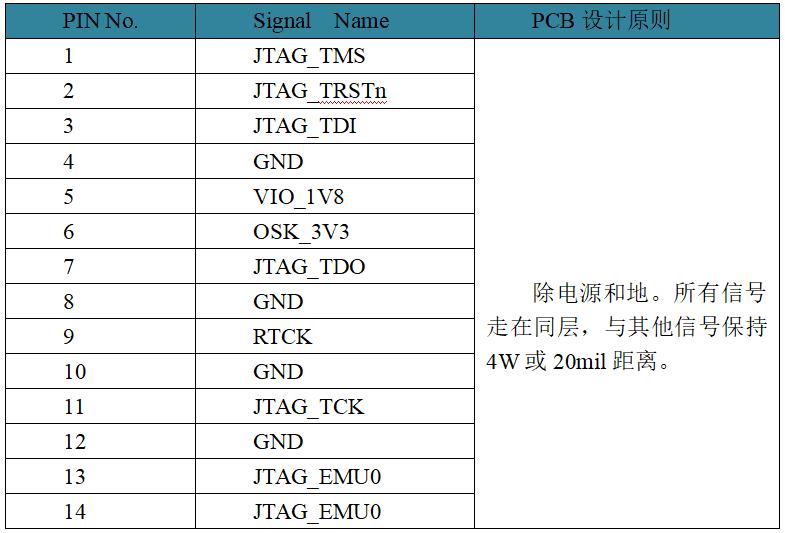

(七)JTAG调试接口

开发板提供了14 pin的JTAG调试接口,信号直接与AM335x连接,让开发人员能通过JTAG口直接调试程序。

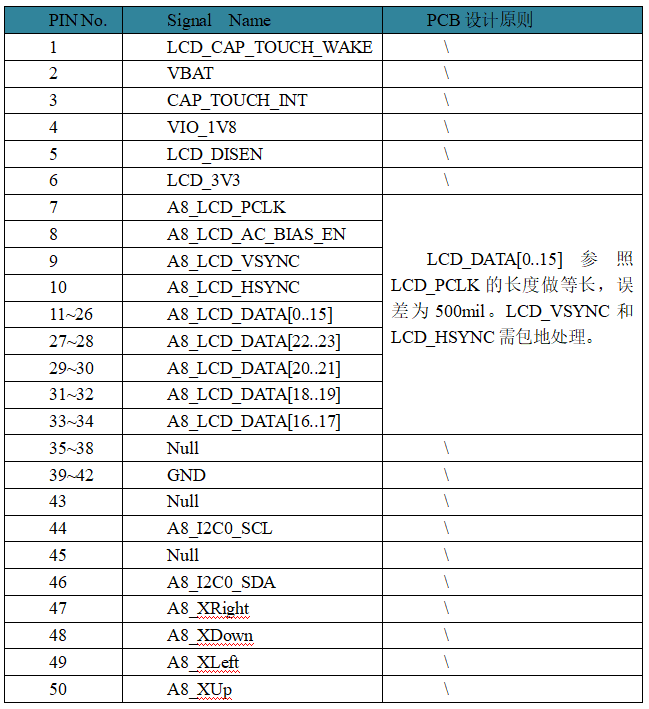

(八)LCD外扩接口

LCD外扩接口支持24bit RGB信号,带有触摸控制信号外接,以及可通过I2C对外接LCD屏进行控制配置。

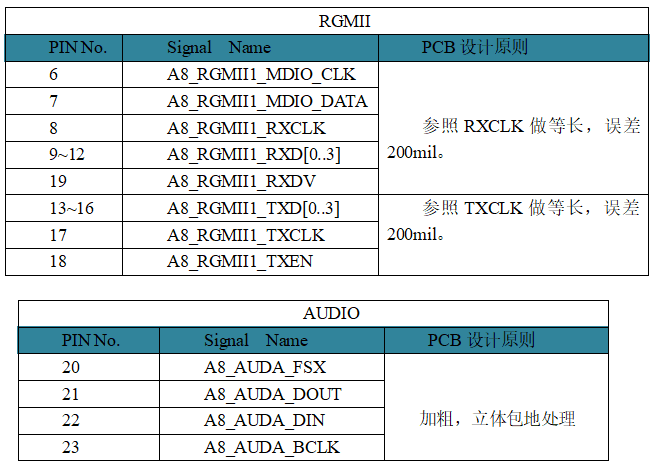

(九)网口与音频外扩接口

AM335x的RGMII和音频接口通过板对板接口外接到另一块功能板上,用户可以根据需求决定是否需要或者需要的哪种功能的板(如百兆网卡or千兆网卡)。

(十)GPMC总线、SPI、McASP总线、串口

核心板通过2个50 Pin板对板连接器对GPMC总线、SPI、McASP总线、串口的扩展,用户可配合对应的功能板进行这类接口的调试。在PCB布线时,注意将同一类型的信号线采用同组同层的布线方式,并且要与其他信号保证至少3w的间距。

三、我的高速PCB设计视频教程

以上文章通过对AM335X工控核心板各电路模块的PCB设计介绍,可以让读者熟悉AM335X平台的PCB设计原则,以及Altium designer设计8层板的设计流程。在此,强烈推荐大家关注我的原创高速PCB设计视频教程。

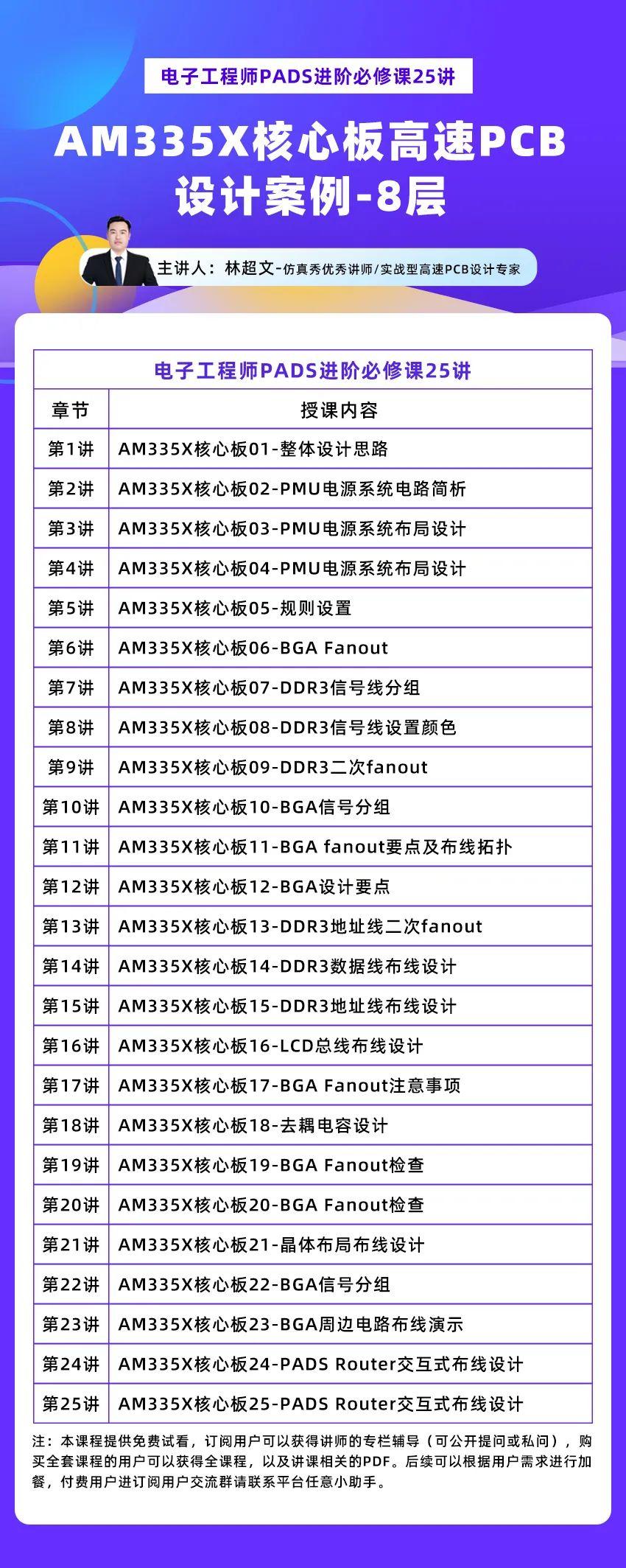

AM335X核心板PCB设计|PADSVX2.11|八层板高速PCB设计案例

我的课程安排

电子工程师PADS进阶必修课25讲:AM335X核心板高速PCB设计案例实操

此外,笔者为所有订阅用户提供知识圈答疑服务和VIP用户交流群。并附赠课程相关资料等(平台支持自行开具电子发票)。

1、用户得到

通过本课程的学习,可以得到以下知识:

(6)赠送课程有关模型资料练习

2、适合那些人学?

③ 从事高速PCB设计行业的新人

四、5G高速PCB互连仿真与PCB设计

4月22日19时30分(周六),笔者受邀在芯片设计仿真第五场讲座带来《5G高速互连仿真技术与射频毫米波PCB设计》,以下是直播安排:

芯片设计仿真(五):5G高速互连仿真技术与射频毫米波PCB设计-仿真秀直播