自动化建模和优化112G封装过孔——封装Core层过孔和BGA焊盘区域的阻抗优化

- 作者优秀

- 优秀教师/意见领袖/博士学历/特邀专家/独家讲师

- 平台推荐

- 内容稀缺

导读:移动数据的迅速攀升、蓬勃发展的人工智能及机器学习(AI / ML)应用,以及 5G 通信对带宽前所未有的需求,导致对现有云数据中心的服务器、存储和网络架构形成了巨大压力。这些颇具挑战性的应用需要高 I / O 带宽和低延迟通信的支持。112G SerDes 技术具有卓越的长距性能、优秀的设计裕度、优化的功耗和面积,是下一代云网络、AI / ML 和 5G 无线应用的理想选择。由于更小的 UI 和更低的 SNR,在采用 112G 数据速率的过程中会遇到更大的挑战。解决这一问题需要综合考虑 RX / TX 规范、串扰、抖动、码间干扰(ISI)和噪声等多种因素,IEEE 标准也推出了通道运行裕度(COM)和有效回波损耗(ERL)作为测量标准,用于检查高速串行系统的互操作裕度。

体现到信号完整性工程师的实际工作中,一项重要内容就是要分析和优化无源链路中的阻抗连续性和不同信号之间的串扰。封装基板上的Core层过孔和BGA焊盘区域,是封装上影响最大的阻抗不连续段,同时,这个区域因为有比较长的过孔纵向耦合,也是最容易引入串扰的地方,是我们需要重点优化的。本文我们将聚焦封装Core层过孔的阻抗连续性优化。

一、封装过孔区域的阻抗特性分析

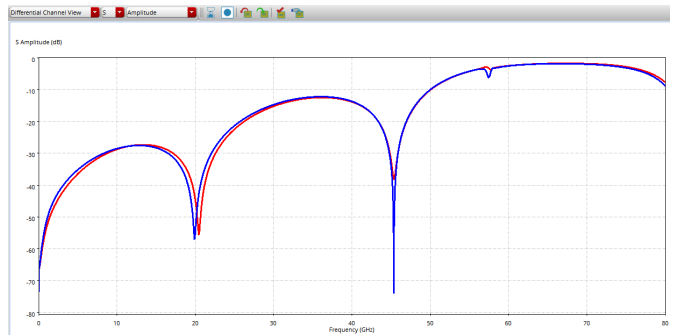

下图是一个典型的封装Core过孔和BGA焊盘区域的差分回波损耗结果。在奈奎斯特频率以下的差模-差模回损都已基本控制到-20dB以下。

我们再看下其对应的TDR结果。可以看到实际阻抗并不是很靠近目标值90欧姆的一条直线,而是存在多个阻抗不连续点。

我们可以结合Layout结构来理解其中的各段阻抗变化。首先看下阻抗最低的D点,这个地方对应的是BGA焊盘区域。一般要控制差分阻抗90欧,差分走线的线宽在25-30um左右,而BGA焊盘的直径会有500-600um,所以这里最容易出现阻抗偏低的情况,需要把相邻的几层平面挖空。

另外一个阻抗较低的B点是Core层过孔的焊盘位置。这个焊盘的直径一般是250-350um,也是比走线线宽高 了一个数量级,所以这里也要对相邻几层的平面做挖空处理。

C点区域是Core过孔的筒身部分。这部分会根据不同的筒身高度(Core层厚度)、相邻层挖空大小/层数、周围回流地孔的距离/数量等体现出容性或者感性。

最开始的阻抗较大的A点是走线在回流平面挖空区域部分。这个地方因为相邻层都挖空掉,按照差分线宽量级的宽度布线,就会出现实际阻抗比目标值高的情况。

二、封装过孔分析案例自动化建模

如上所述,封装Core层过孔和BGA焊盘区域的多个布线参数都会影响这段链路的阻抗连续性,而且链路上不同组件对这些参数的调整方向需求有的还相互冲突,需要综合权衡。这么多参数需要调整,不可能把所有的组合都先在封装工具中设计出来再逐一用仿真工具提取模型进行分析。比较常见的做法是由资深的SI工程师根据经验判断最关键的参数和大致的取值范围,请封装设计工程师做几种不同的场景,然后在这基础上把各层挖空大小做成变量进行扫描,或者根据仿真结果手动迭代调整参数。但是,这种做法存在很多限制:首先是严重依赖资深工程师的经验;其次是受项目交付周期限制,实际能覆盖到的参数组合和调整范围空间都比较有限;最后,如果出线层、叠层、材料、管脚排布、信号速率等发生变化,这些参数调整的结论不能直接复用,重新建模分析又非常消耗时间。

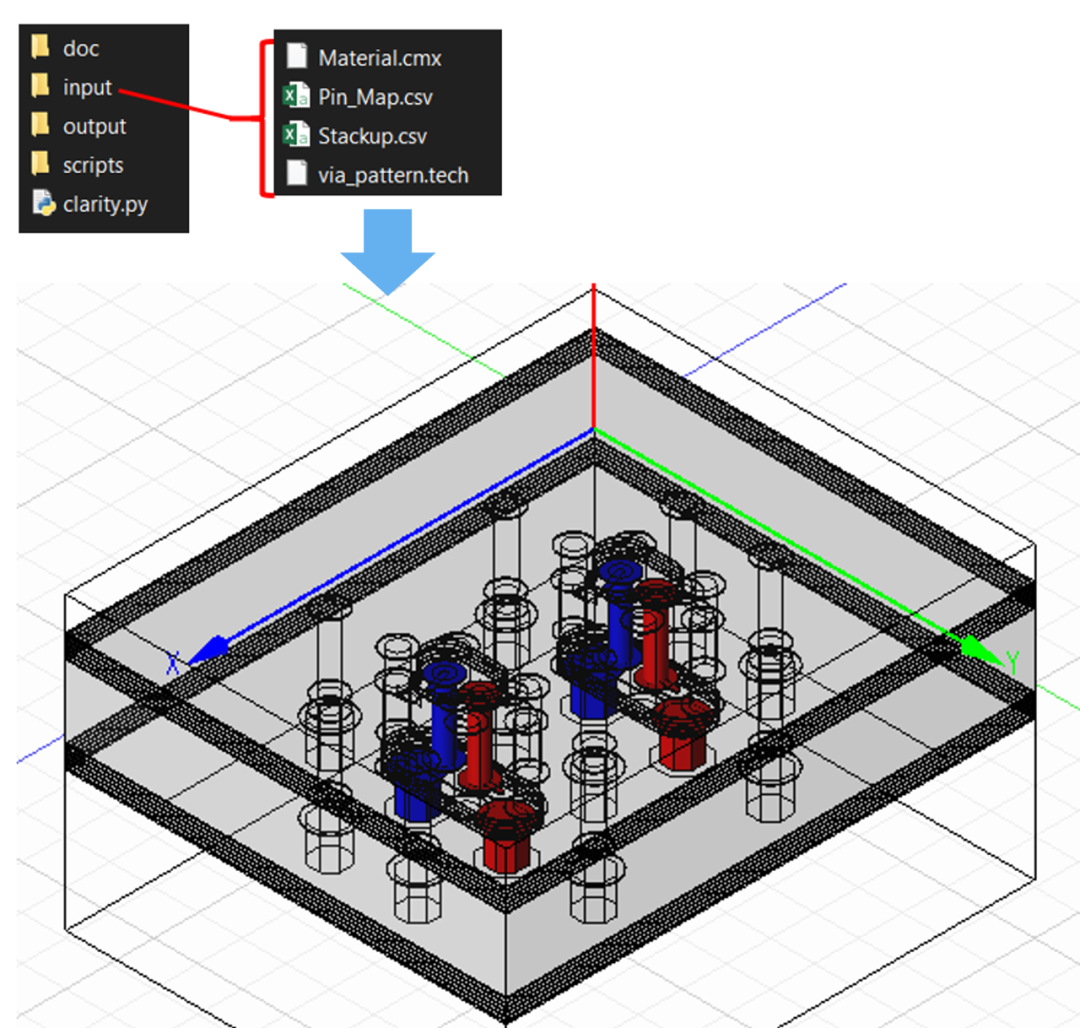

笔者的做法是利用仿真工具强大的参数表达式功能,编写Python脚本,读入PadStack、叠层材料、Pin Map等信息,自动创建封装过孔优化工程,把上述各种参数,包括过孔间距、挖空区域大小、挖空层数、回流过孔方式、回流过孔距离、挖空区域走线线宽等,都在模型中做成可扫描的参数。这样,调整参数时只要在仿真工具中修改数值,整个仿真结构也会跟着改动,不需要返回封装设计工具进行调整,更加方便快捷。而且,不管叠层、材料、管脚排布等如何变化,只要简单修改输入配置文件,十分钟就能完成新的仿真工程建模。

三、设计参数自动化/智能化调整

完成仿真工程建模后,下一步就是要调整设计样式的选择和各设计参数的取值,以优化阻抗连续性和串扰大小。这里会遇到一个问题,就是由于参数数量多,每个参数还有各自的取值范围,即便SI工程师根据经验固定某些参数的数值或者绑定不同参数同步变化进行简化,各参数排列组合后的取值空间很可能依然是巨大的。以5个独立变量,每个变量10个扫描数值来计算,排列组合的取值空间就达到10^5=100,000个,这个数量级根本不可能在实际项目交付过程中去遍历。即使是每个变量只有5个扫描数值,排列组合的取值空间也达到5^5=3125个,很难遍历完成。因此,一般的做法还是需要SI工程师手动进行”调整参数”->”仿真”->”分析结果”->”调整参数”->”仿真“的迭代,受到项目交付周期和有效仿真/分析时间的限制,实际能完成的迭代次数非常有限,通常都不见得能找到最优解。

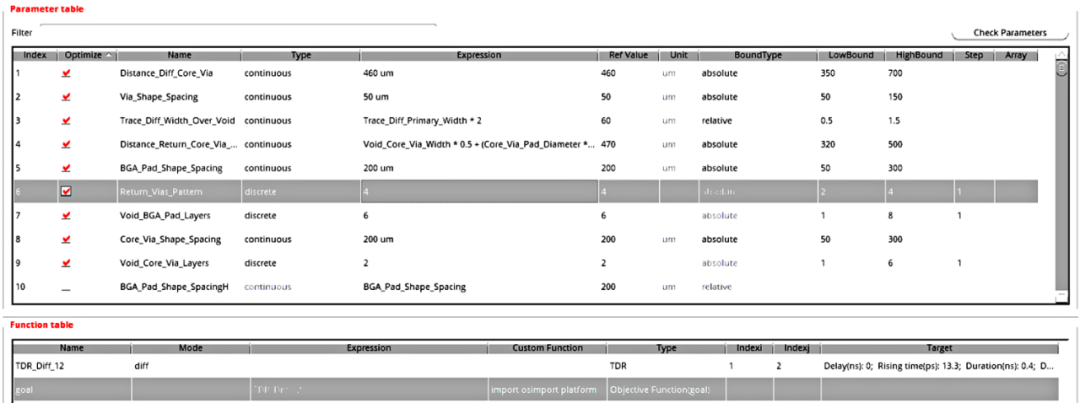

随着仿真工具的发展,现在调参这个难题可以交给AI引擎来自动实现。这里我们利用Cadence最新推出的Optimality Intelligent System Explorer智能优化引擎来完成封装过孔优化。在Cadence Clarity 3D Solver仿真工具中打开通过脚本创建出来的仿真工程,通过菜单栏命令打开Optimality Explorer优化引擎,接下来只需要设置好需要调整哪些参数、每个参数的取值范围,然后定义好我们要优化的目标、设置并行跑的任务数量和仿真服务器资源,剩下的就是等Optimality Explorer根据机器学习算法自动完成” 调整参数”->” 仿真”->” 分析结果”->” 调整参数”->” 仿真 “的迭代,最终得到我们想要的优化结果了。

值得一提的是,Optimality Explorer除了官方给出的一些常用的插损、回损、串扰、TDR等优化目标,还支持Python接口,可以用Python自定义任意的目标函数,比如本例我们用了自定义的TDR指标作为优化目标,综合考虑了TDR结果中的阻抗偏差最大值、阻抗偏差峰峰值、偏差阻抗长度等指标。

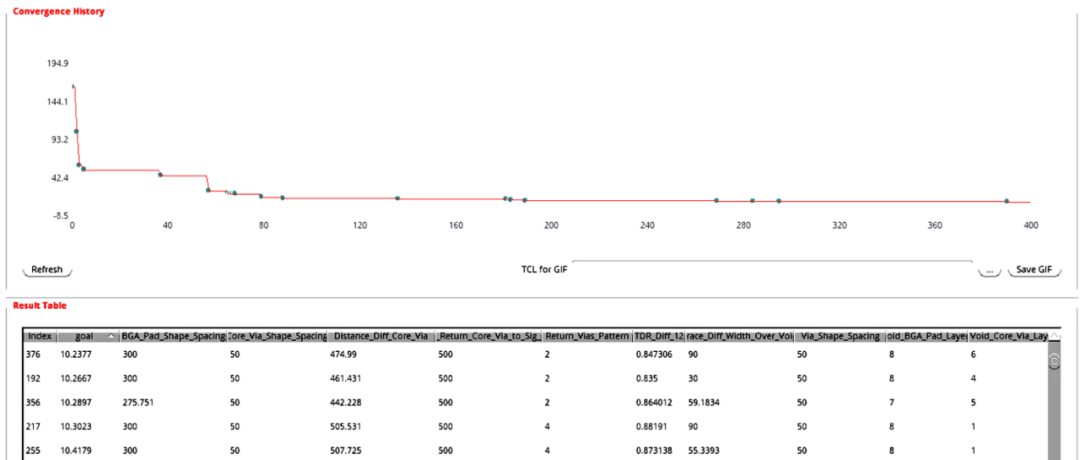

Optimality Explorer的收敛曲线如下。经过几十次迭代后,得到的仿真结果TDR指标就已经优于工程师手动迭代的结果。因为是工具自动调参,不需要工程师干预,我们可以按原定设置最大迭代次数继续进行优化,进一步得到更优化的结果。

(完)