信号协议编码_PCIE3一致性测试编码

前两篇文章为大家介绍了一些编码的原理,这也为仿真和测试时所用的码型提供了参考;

这篇文章我们来看一下PCIE信号在做TX一致性测试时,所采取的码型;

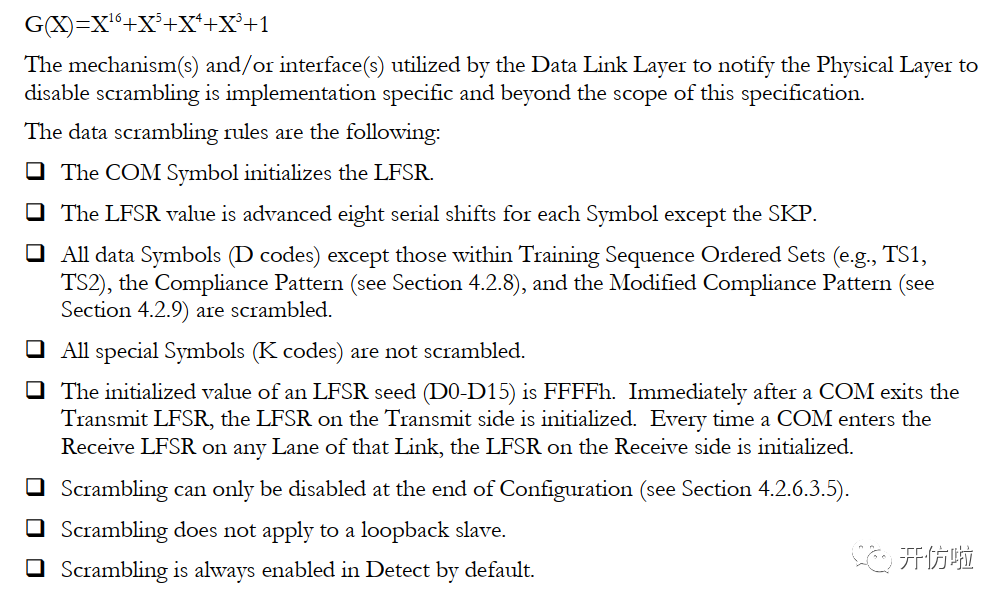

先来看一下,PCIE1.0和PCIE2.0采用8b/10b编码,编码前先进行扰码,扰码器和扰码器的种子(初始值)如下:

PCIE3.0采用128b/130b编码,编码前先进行扰码,扰码器和种子(初始值)如下:

下面来看一致性测试码型

这些码型在PCIE协议规范中有明确规定,我给摘了出来,并用仿真软件演示出这些码型;

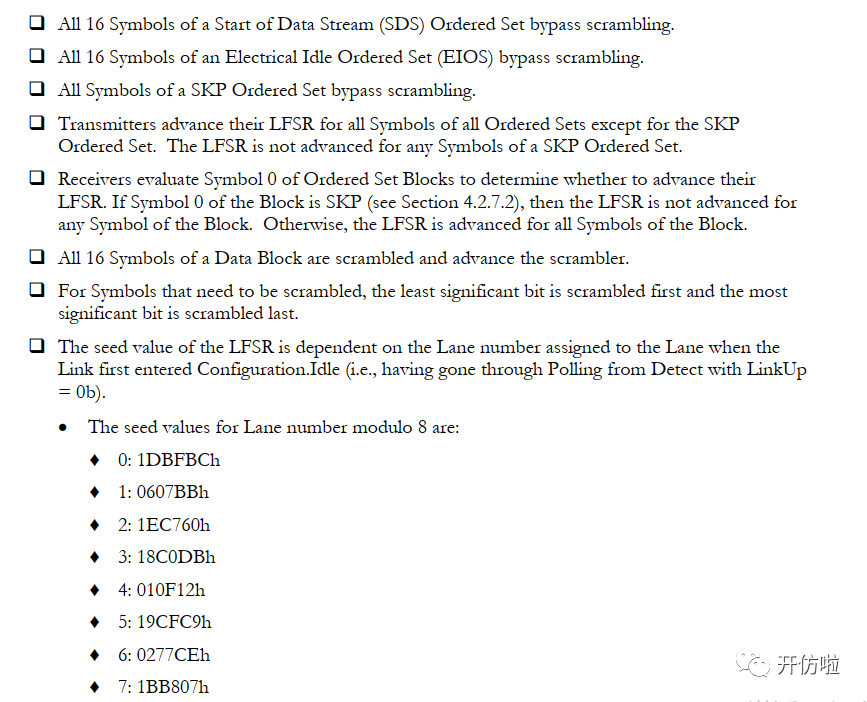

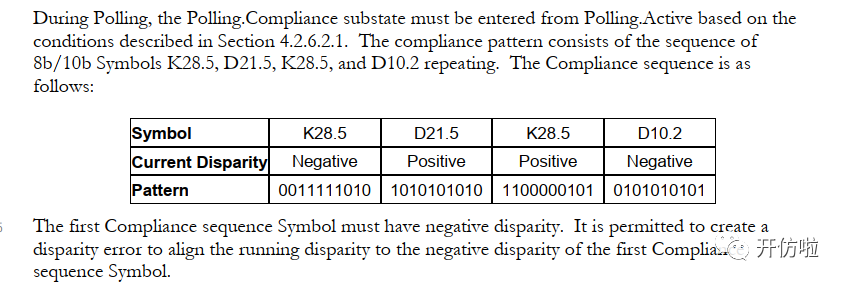

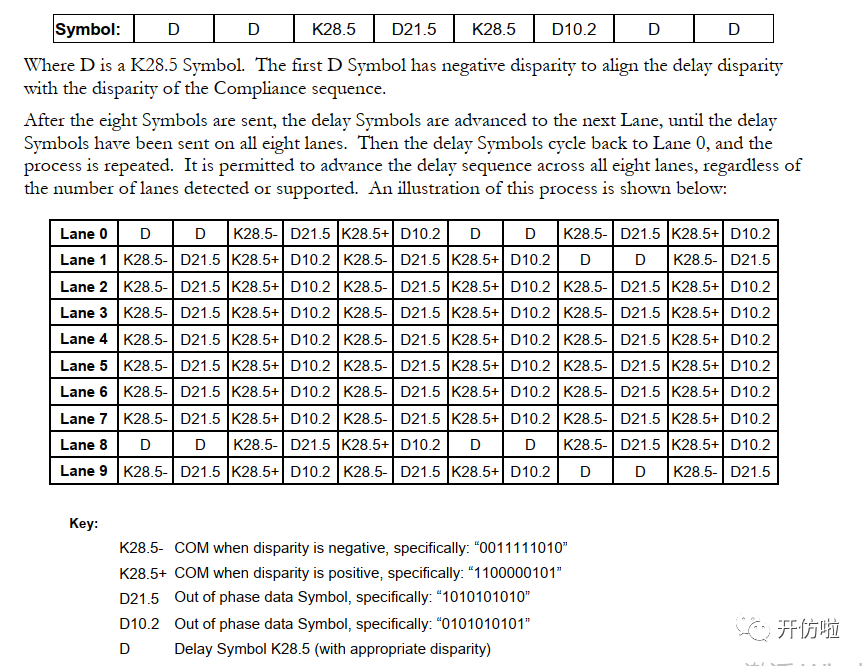

PCIE2.0/1.0协议内容如下:

大概意思就是,测试码型为重复的8个symbol,D D K28.5- D21.5 K28.5+ D10.2 D D,D也是K28.5,第一条lane(lane0)的8个symbol发完后将这8个symbol传递到第二条lane上,以此类推一直到第八条lane又回到lane0,如果是X16的,后面的八个和前八个一样,每条lane发送完这8个symbol后,即是重复的K28.5- D21.5 K28.5+ D10.2

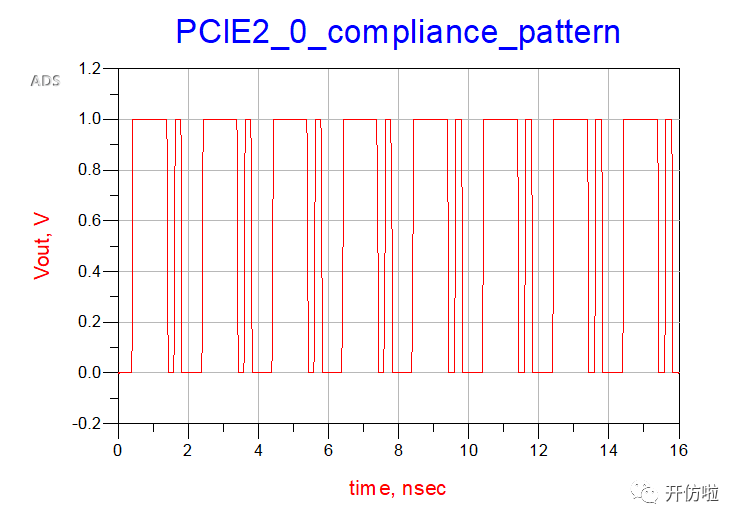

协议还规定了修正后的一致性码型如下(略有不同):

由原来的4个基本symbol变为8个,K28.5- D21.5 K28.5+ D10.2 err err K28.5- K28.5+,delay标识则是在前面加上4个D,在后面加上4个K28.7;

err是个8bit字节,应该做的是奇偶校验,如果有错误,bit7为1,否则为0,bit[6:0]为错误个数,如果没有错误,这个symbol为00000000,编码后为1001110100(-)和0110001011(+);

这样看还是比较抽象,我们用仿真软件来看一下测试码型波形如下:

下面来看PCIE3.0一致性码型

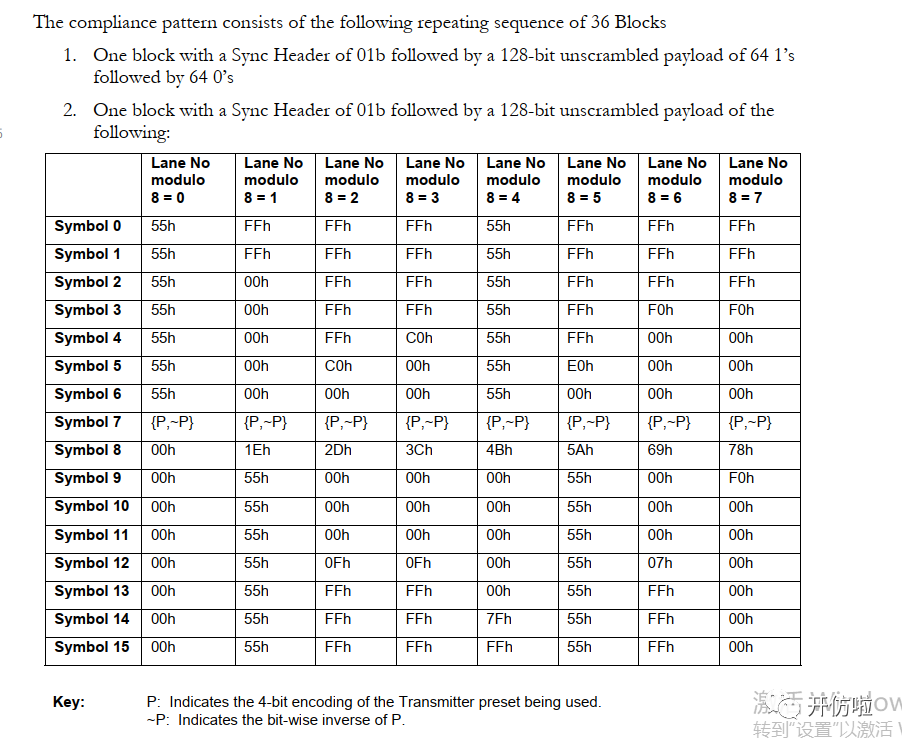

协议内容如下:

该码型共有36个block,后面重复这36个block;

第一个block为01的header,后面是64个bit1,在后面是64个bit0;

第二个block为01header,后面是表中的序列,symbol7的前4个bit是preset值,后4bit极性和前四个相反;

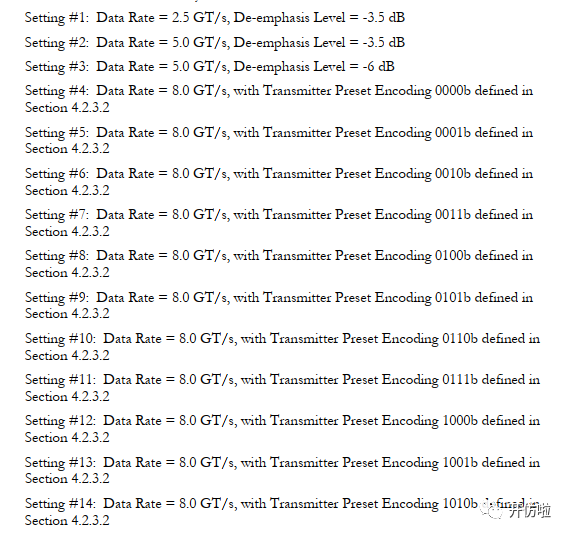

Preset对应的序列

第三个block为01的header,后面是表中的序列;

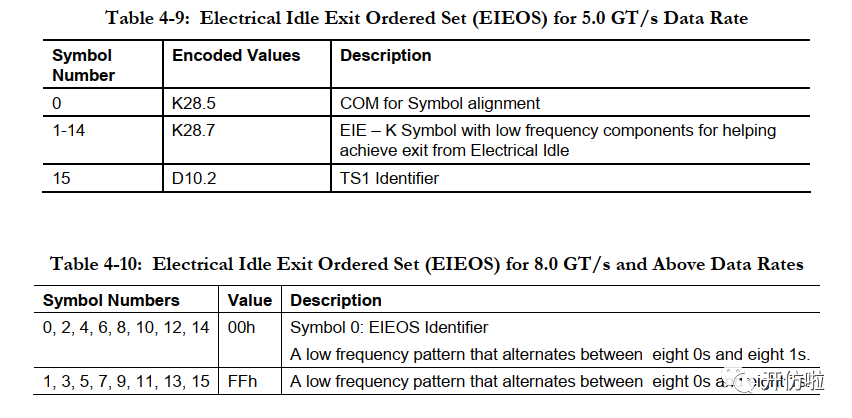

第四个block为EIEos,这是一个order set,序列如下:

这个block即为10 00000000 11111111 00000000 11111111…… 共130bit

后边是32个相同的block,每个block都是16个扰码后的IDL(00h),即为16个01011100;

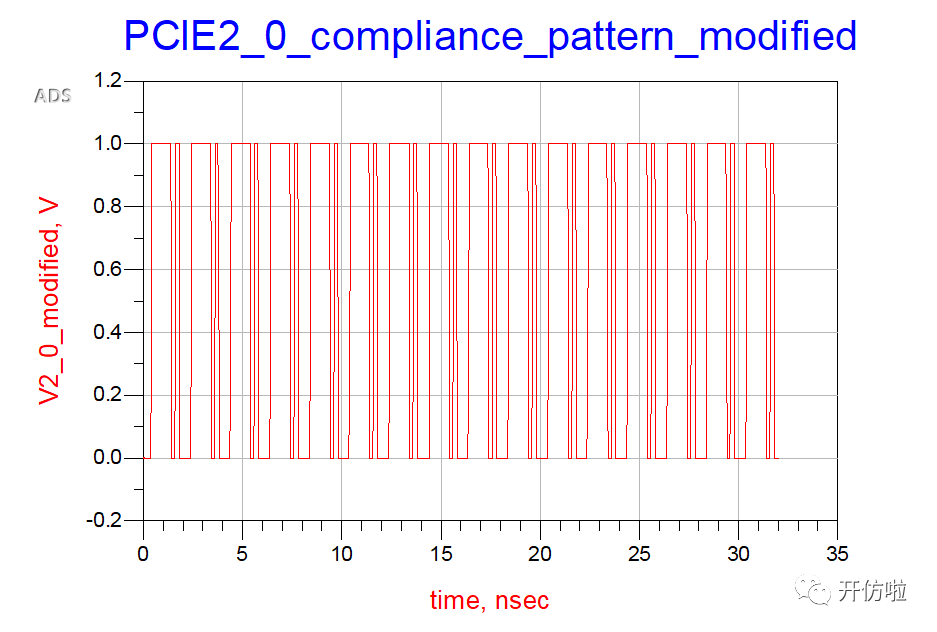

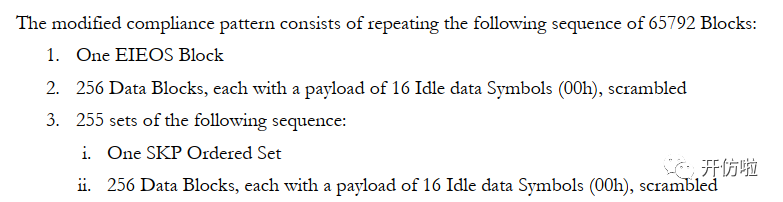

PCIE3.0也有修正后的码型:

一共65792个bclok;

第一个是EIEos block,同上;

接下来是256个相同的数据block,每个block都是16个扰码后的IDL(00h),即01011100;

再接下来是255个循环,每个循环由两部分组成

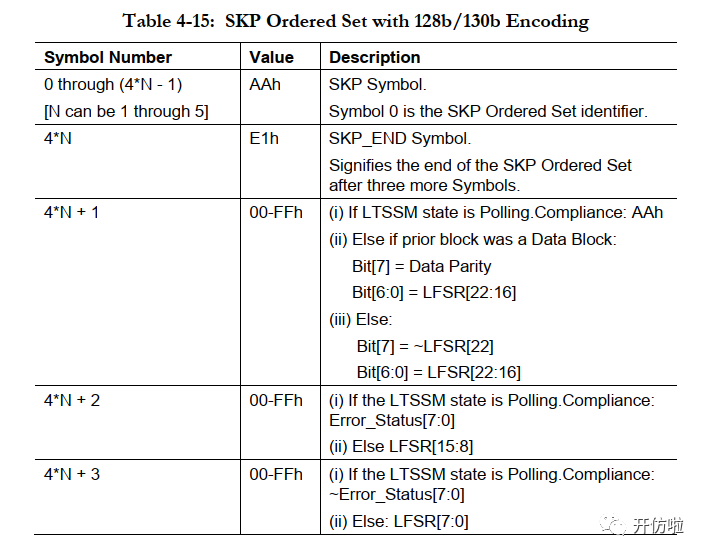

第一部分为一个SKP ordered set,如下图,码型中的symbol应该也是16个,所以N等3,所以symbol0~symbol11为AAh,即10101010,symbol12为E1h,即11100001,symbol13为AAh,即10101010,symbol14为eer_status,没有err为00000000,symbol15也为00000000;

第二部分是256个相同的数据block,每个block都是16个扰码后的IDL(00h),即01011100;

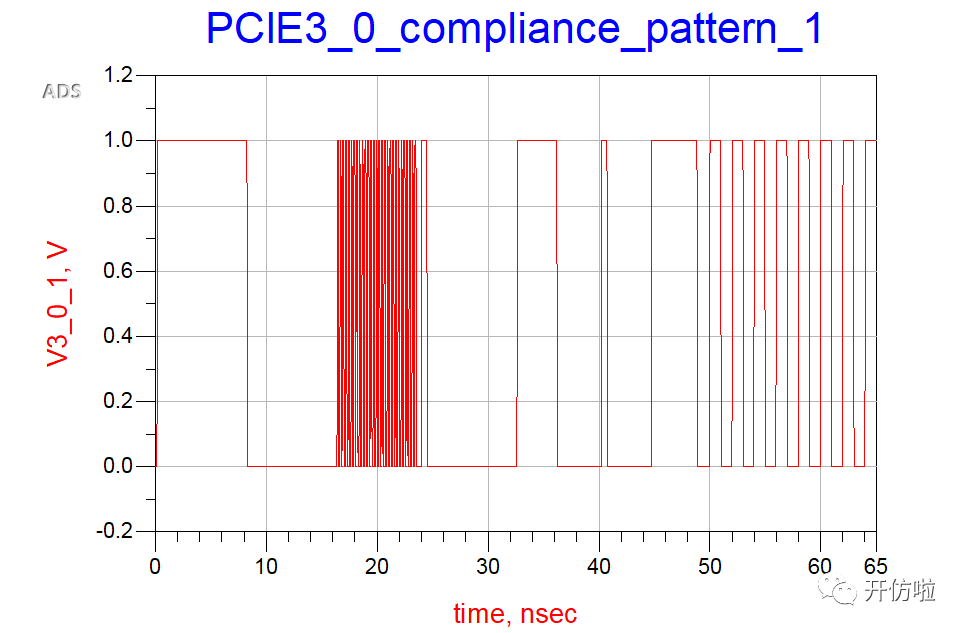

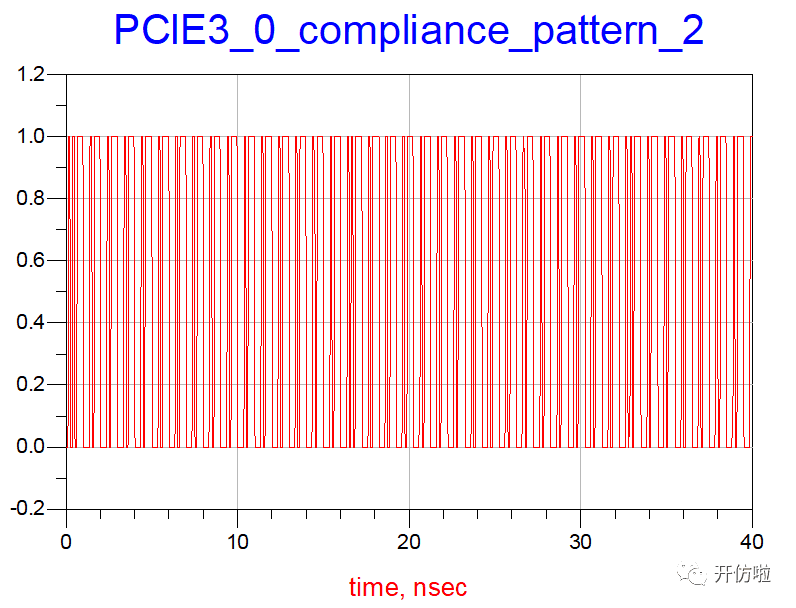

同样用仿真软件来看一下波形如下:

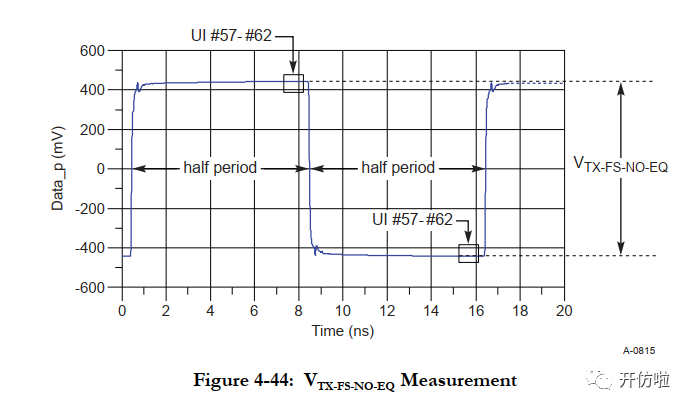

一致性测试软件分别采集这些码型,用来做不同的信号分析,如眼高、眼宽、抖动、幅值等;

下图就为协议中采样64个bit1,在后面是64个bit0,来分析信号在没有任何均衡时的摆伏:

下篇文章为大家介绍USB3.0和USB4.0协议的一致性测试码型;

推荐阅读

信号包地反而更差

AC耦合电容对信号的影响