“顶梁柱”式人才短缺,13年EDA老兵带你实操3D器件模型数字化

- 作者优秀

- 优秀教师/意见领袖/博士学历/特邀专家/独家讲师

- 平台推荐

- 内容稀缺

导读:6月29日人民日报刊文《壮大国产工业软件》。这一消息的发布立刻引起了各大媒体的转载,对于中国国产工业软件的软肋,官媒发声意义重大。而目前的中国正如人民日报刊文所言“我国正加快推动由制造大国向制造强国转变,作为智能制造的关键支撑,工业软件对于推动制造业转型升级具有重要的战略意义”。简而言之没有国产的工业软件,中国的制造业转型升级将举步维艰,工业软件才是智能制造的“魂”。

一、工业软件是智能制造的“魂”

首先,老吴来带大家来理解一下,什么是智能制造?

智能制造从专业的角度看,其实就是在生产过程中将智能设备通过通信技术连接起来,实现生产线全自动化。

而这一网络同时包括了各类传感器收集生产制造过程中的各种数据,通过通信网络,传输到工业服务器中。这些数据将在各类工业软件系统下进行详细的数据分析,优化生产流程制定个性化生产流程,最终实现智能化生产。

那么为何我们要发展智能制造呢?众所周知,提高产品质量、降低成本、缩短研制周期,是制造业企业发展壮大的三大要素。而要解决这三大问题,智能制造必不可少。例如智能制造可以降低生产故障率,据统计数据显示,90%以上的生产故障都是可以通过工艺设计解决。而生产故障的降低,必然离不开先进的智能制造系统。而智能制造的前景相信不用笔者多加阐述了,在目前的制造业中,智能制造已经是大势所趋。

二、工业软件人才缺口大

在智能制造发展迅速的今天,中国智能制造领域的人才缺口却非常之大。据权威机构的的统计,2020年智能制造领域人才需求大约在750万左右,而人才的短缺量将在40%左右,缺口在300万人以上。而据专家的预计,这一数据随着中国对于智能制造的关注,这一比例在2025年很可能超过50%。

人才的短缺也直接导致了现在的局面“90%的芯片、70%的工业机器人、80%以上的核心工业软件依赖进口。国内制造业企业智能制造转型成本居高,作为制造业根基的小微制造业企业,智能制造转型更是举步维艰”。

而智能制造 “顶梁柱”式人才的短缺,主要体现就在工业软件。以近期华为被美国禁用的EDA软件为例,据权威机构的统计数据显示,我国约有1500位EDA软件开发工程师。

而据国外媒体的报道,EDA巨头Synopsys公司软件开发工程师就有7000余人,从这个数据对比我们不难看出我们的差距。

前路漫漫,道阻且长,行则将至,做则必成!

作为一名在EDA领域摸爬滚打13年的老兵,老吴对于这一现实感受更为深刻。

老吴在这里就根据个人的工作学习经验,与大家分享一些3D器件模型库的导入及管理经验,希望可以帮到那些渴望全面实现设计验证数字化,又苦于在导入3D模型过程中遇到各种问题的朋友们,希望可以帮助您拨开迷雾,加速个人及企业的发展。

三、器件3D模型库的创建及管理公开课

在从原始的2D器件库全面升级到3D器件库的过程中,很多公司和科研单位都遇到了不少的困难。可以直接导入的模型资源比较少,复杂的模型设计耗时费力,模型校验不够准确,人力资源不足等等,都成为各家公司向数字化进军路上的绊脚石。

电子产品先进设计第一讲:3D器件模型的工程实践案例-拔开迷雾,助力电子产品设计验证数字化

四、老吴为什么推荐学习SiP封装?

SiP封装设计是一门多学科高度交叉的前沿学科领域,其设计、制造和应用广泛涉及到物理学、化学、力学、微电子学、电子学、光学、生物医学和控制工程等多个学科。

传统的芯片设计中,往往重视前端代码级和后端网表以及布局布线信息的仿真和验证,对芯片封装、以及芯片安装在PCB电路板系统后的工作情况验证较少,难以准确考虑外围封装与PCB对芯片功耗和噪声的影响。

MENTOR的芯片,封装和PCB系统协同设计仿真方案,允许工程师在芯片设计的初始阶段就考虑外围封装和PCB以及整个系统的影响,并针对各个信号链路进行整体优化。

SiP的优势包括用户IP集成、IP复用、混合模拟/数字设计、设计风险低、集成大型存储器、降低工艺复杂性、降低开发成本和缩短上市时间。

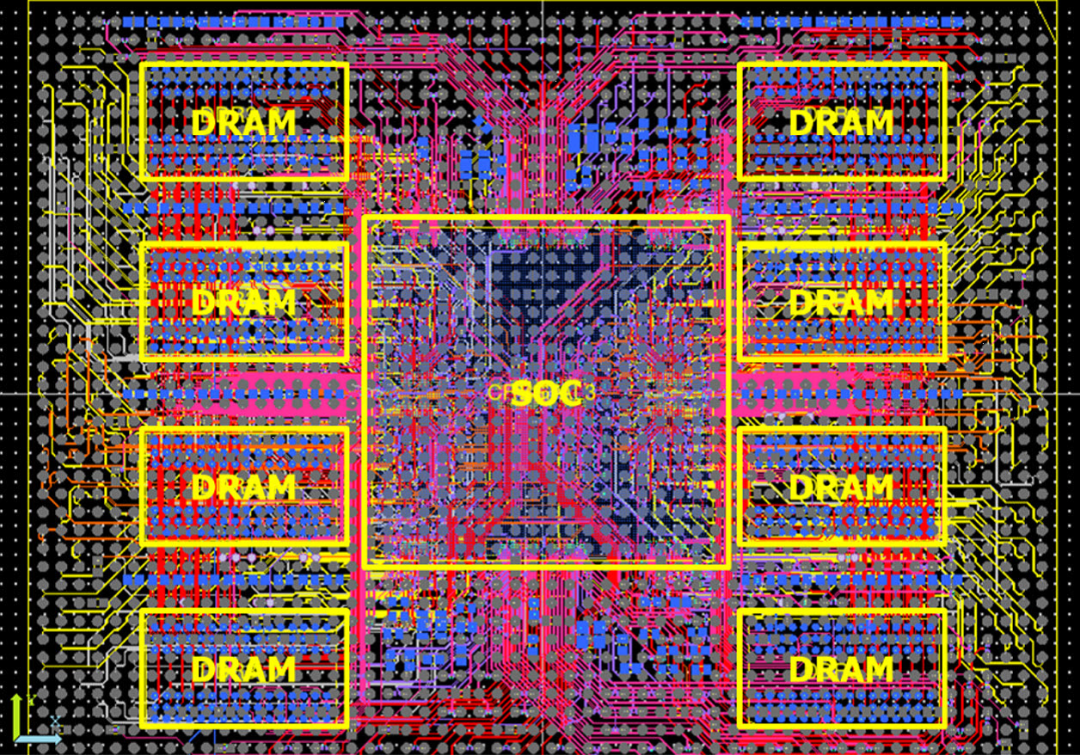

图1利用Package Designer快速完成复杂SiP设计图

3D封装设计

老吴以传统的Wire bond工艺入手,系统地讲解了Chip-on-Board、Stacked Die、嵌入式芯片、3D DRC 以及无源器件的封装设计方法,SiP设计提供从原理图到板图、信号完整性SI分析、电源完整性PI分析以及thermal热分析的全套解决方案。充分展现了xPD对于复杂SiP系统设计更有独到的优势。

主要学习点:

Die Wizard工具提高裸片库创建的效率; 复杂Bonding Wire 的参数化自动生成; 多级腔体设计; 自动生成Power Ring; IC Die堆叠设计; 精确Bonding Wire 模型创建,帮助提高产品良率; 实时3D DRC检查。

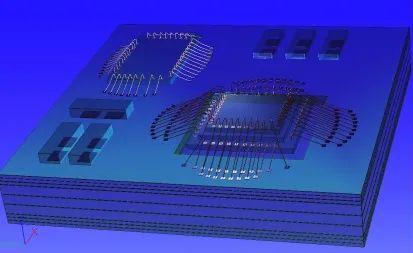

图2 多芯片3D堆叠效果图

信号链路优化

老吴在第9讲中引入了Xpedition® Substrate Integrator这款工具,此产品可透过中介层和封装自动协同设计规划和优化单个 IC 或多个 IC 间的连通性,同时以不同的 PCB 作为目标。设计人员和架构师可以快速轻松地组装完整的跨领域基板系统,并透过以规则为基础的方法来驱动BGA管脚规划和管脚优化。

主要学习点:

利用跨领域管脚/信号进行系统级逻辑验证,对跨领域复杂路径进行优化; 多基板组装在单一界面中进行系统设计; 设计器件与资料库的层级式管理; 多种文件格式的器件输入输出

图3信号链路优化示意图

系统级设计

SiP设计不单单局限于自我内部的具体设计,与外界其它IC和PCB设计关联也十分紧密。如果想设计一个高度优化的电子产品,对于各个信号的整体链路优化是必不可少的。老吴从第15讲开始,为大家讲解并演示了如何创建及管理系统设计工程。

主要学习点:

在单个视图中实现跨域互连可视化 自行定义pin的规则和ball-out分配 动态单元定义 多模物理布局

图4强大的系统级封装设计流程图

设计文档输出

SiP设计好并完成必要的检查后,需要将设计数据转化为可制造的生产数据。本章节将会详细介绍如何输出生产及项目存档的必要文件。其中包括了SiP 基板制造文件,贴装文件,第三方设计评审文件,装配文件等等。

可以使读者充分了解设计与生产之间的紧密关系,不仅做到知其然并且知其所以然,帮助大家成为一名优秀的设计人员。

实际案例

老吴系统地讲解了从Die的创建或导入,BGA管脚定义,多层级网络互连优化,直到Die,Interposer,BGA封装以及PCB联合设计系统。满足各种实际设计需求。

以上是笔者关于SiP从库创建到设计过程中各个环节的详细介绍,希望对大家有所帮助,如有不当,欢迎批评指正。

作者:吴岩,仿真秀专栏作者

作者简介:2007年毕业于沈阳航空航天大学电子信息工程专业。曾在多家国际知名公司从事通信服务器及终端产品研发工作,后担任索尼移动EDA部门整体环境建设及优化设计流程工作,对大中型企业EDA的设计和验证环境的搭建有着丰富的经验。2015年加入Mentor Graphics负责中国华北区板级解决方案技术支持业务,为客户提供综合板级解决方案,先进技术导入、应用培训等技术咨询及支持。