华为芯片堆叠封装设计专利刷屏,请和我一起仿真计算和验证

图片来自半导体媒体观察

导读:近日一篇《华为又一项芯片堆叠封装专利曝光》的文章刷屏芯片封装工程师的朋友圈。它是一个避免使用TSV的3D封装设计,吸引了我的芯片封装设计精品课学习型仿真工程师的好奇和关注。众所周知,TSV的制作工艺复杂,可靠性差,尤其是TSV first和TSV middle都需要在fab厂做,甚至会影响芯片器件可靠性,今天我们就来聊聊芯片堆叠封装那些事,本文基于笔者这些年对芯片封装的理解和操作经验摸索出来的,水平有限,不当之处请大家多批评指正。

一、华为芯片堆叠封装

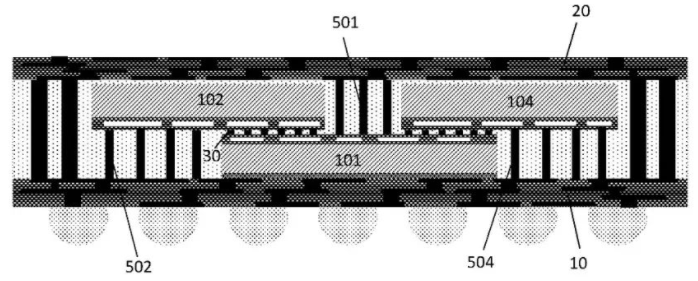

华为的这个专利内容如下图所示,自左向右一步一步开展。首先是下芯片部分。将各个芯片做好RDL和bump或者UBM(Under Bump Metal),然后face to face焊接一起。但是要注意芯片之间要错开,芯片需要沟通的部分焊接在一起,而其他有源部分要露出来,方便下一步操作。各芯片连接之后,通过molding将这些芯片都封在一起,然后在EMC(Epoxy Molding Compound)上做过孔,这可比TSV(Through Silicon Via)容易多了。然后在EMC两面都可以再次RDL,然后上面做UBM和bump。最后可以将其焊接到基板上,然后最上面的芯片也焊接到这个装配体上,这就完成了3D封装装配。

3D封装是在后摩尔时代为了让芯片集成度更高,在同一种制程下,3D封装可以保证相同面积下芯片有更强计算能力与传输能力。但是3D封装面临一系列如SI(Signal Integrity)、PI(Power Integrity)、Thermal,Mechanical等问题。

要解决的是不同功能芯片之间信号传递功能,要求信号路径尽可能小来保证SI要求。其次要保证芯片供电,对于在“楼上”的芯片来说,电源距离增大代表寄生增加,会增加电阻(静态电阻)以及增加阻抗(动态阻抗),导致电压无法满足要求。再其次,3D封装面临散热问题,楼下的芯片由于无法直接与壳接触,导热路径要绕远经过楼上的die(硅导热稍微好些),或者直接通过EMC(导热极差)到壳上。

最后就是力学问题,由于芯片一层层叠起来,由于多层材料CTE(Coefficient of Thermal Expansion)不匹配,而且底层芯片的厚度往往比较低(TSV对底层芯片厚度有要求),会有应力影响bump可靠性性能,甚至硅片crack的情况。

二、华为芯片堆叠封装专利简析

在华为这篇专利里,巧妙的利用molding可以添加过孔的特点,楼上芯片的SI和PI问题可以通过设计解决。不过楼下的face up的芯片,由于没有过孔,需要类似wirebond的封装,信号需要在face面平移一段,这就会导致信号或者电源的极大衰减。

另外楼下芯片的散热问题依然严重,可能需要通过增加过孔,利用过孔的铜材料散热。然后最后就是力学问题,由于带有过孔的molding层内有两层芯片,EMC材料和die材料CTE严重不匹配,难免会有键合的边角处大的应力。总的说来,这篇专利绕过TSV实现3D封装,是很好的设计方案,不过对设计有许多要求。

以上的种种要求,都需要仿真去校核与验证。比如SI和PI问题,是需要用电磁分析软件来辅助设计(比如高速信号用HFSS,PI问题用SIwave),才能保证信号损耗以及阻抗匹配,保证电源的阻抗在需求范围内。散热也有热设计软件(比如ICEPAK),通过计算导热热阻等,获得芯片结温,确保芯片不会过热。而力学可以用ANSYS的mechanical模块,可以通过模拟实际封装工艺流程,确保bump寿命。

三、华为专利的仿真校核和验证

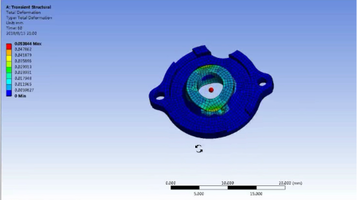

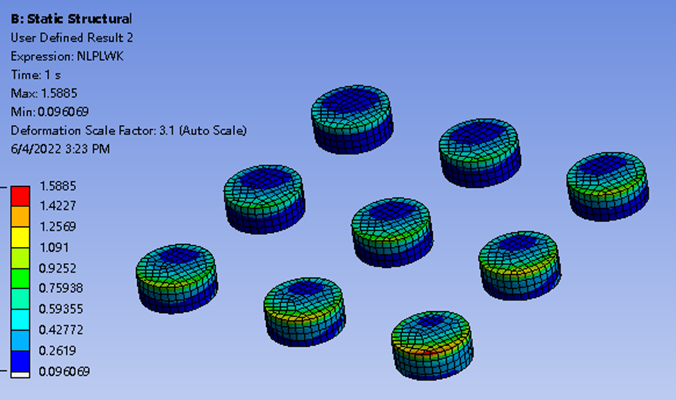

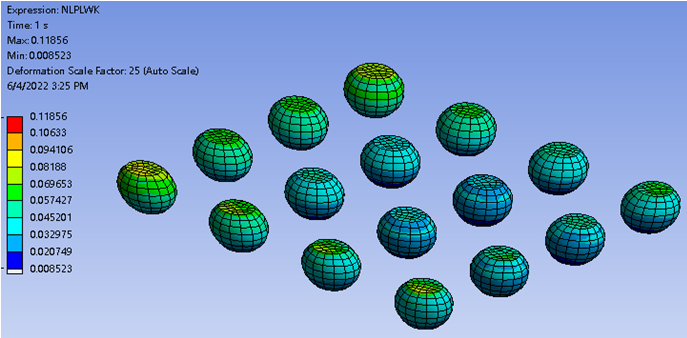

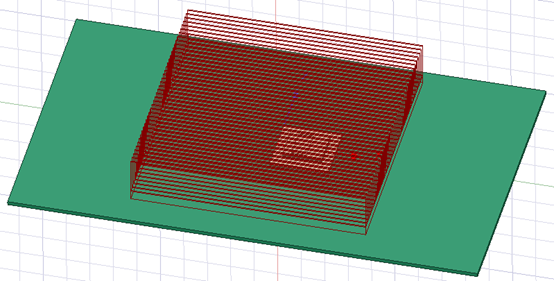

针对华为专利内容,下面做了一系列仿真来对此等结构进行校核。首先最重要的是bump寿命以及warpage,毕竟可靠性不达标性能再好也没有用。本次仿真只如上图叠两个die,在ANSYS Mechanical里面建模。

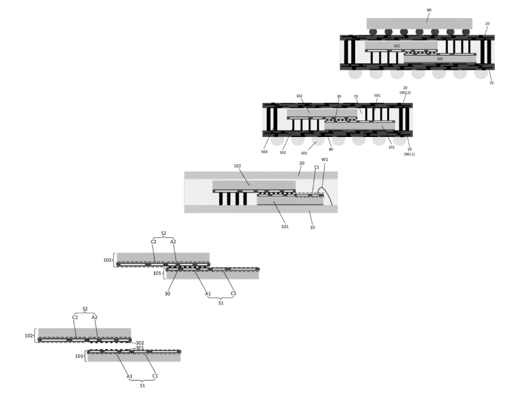

模型大体分三层,楼上,楼下和基板。其中黄色和橘色是硅片,他们之间是bump和underfill,四周由molding材料填充。基板尺寸20mmx20mm,做成对称模型,中间是对称面。Underfill的curing温度是165C,因此计算从165C→25C的力学变化。求解获得warpage如下,

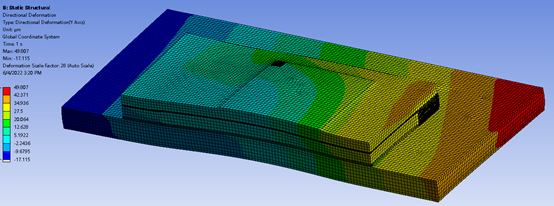

bump的塑性应变能密度的值如下所示,在楼上和楼下之间的bump应变能密度和基板之间的C4 bump比大很多,是易失效的位置,还可以看出在最角落的bump是最容易失效的。另外通过一些公式换算可以通过应变能密度获得其在高低温循环下的寿命。当然,如果只是判断选型,简单对比应变能密度大小即可。

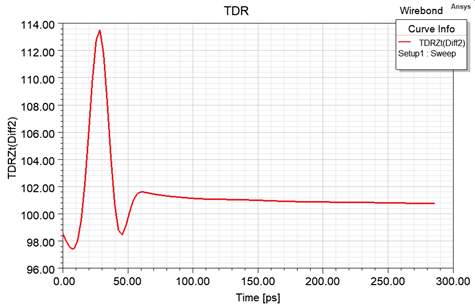

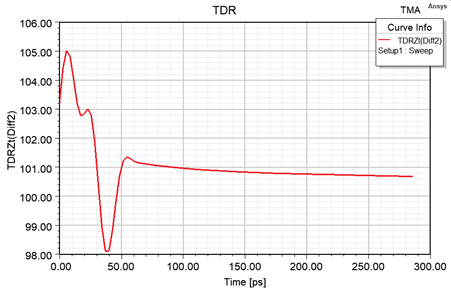

然后就是性能指标。之前说这个结构楼下由于要用wirebond供电以及走信号,肯定不如楼上芯片性能,此处可以用ANSYS HFSS做个验证。如下图所示是楼下和substrate之间电连接,因为wire之间的间距只有100um,阻抗不是很低,实际很难控制到如此说。不过这样走线阻抗也有110ohm以上。

如果是在molding中打孔,因为pitch和孔直径可以更灵活可控,阻抗也可以做的很好,模型以及TDR见下图。因此楼上芯片适合做高速的信号。

除了SI的问题,PI的问题也很重要。PI最基础的评估是IR drop,也就是静态电流产生的压降。如果压降太大,芯片可能供电不够。如下图所示是用Q3D计算的IR drop,不够此处施加是1A电流产生的0.1907V压降,意味着这一根wire是0.1907ohm电阻。

下图是在molding中的通孔带来的压降,是0.1468V。因为长度小以及直径粗,是比wire小一些的。不过实际molding中的孔是可以继续加粗的,而且wirebond只能围芯片一圈,而这种通孔是可以在芯片整个面上增加,因此IR drop要比wire小很多。

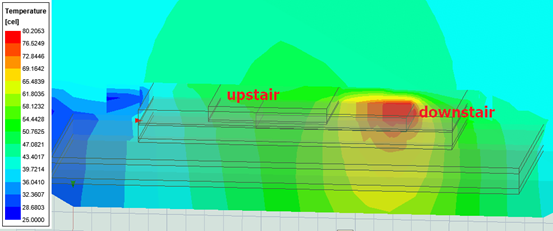

最后就是评估热了。热的模型在ICEPAK中建模,不过是集成到AEDT中的ICEPAK。结构是从上面mechanical中镜像之后导入的。芯片上面贴一个散热器,下面是一个200mmx100mm的PCB。假设只有芯片的上层和下层发热,各自20W,散热器上面流过平均3m/s的风。

下图是截面温度,可以看出楼下的芯片温度很高,80C,而楼上的芯片温度只有50C。只是因为上层芯片的温度直接由散热器导走,而下层的芯片需要经过molding,而molding的导热很差。

为了帮助大家更好的理解和掌握华为专利的仿真校核和验证过程,笔者将模型资料放到仿真秀官网和APP-我的仿真专栏【萧显君】对应文章的附件中,感兴趣的朋友48小时后可以自行下载。

此外,欢迎大家关注我的芯片封装入门进阶精品课《芯片封装仿真41讲-掌握ICEPAK、ANSYS Mechanical和HFSS在芯片封装仿真应用》(持续加餐,点击这里试看)

本课程旨在给大家介绍芯片封装结构的仿真方法,基本囊括了所有芯片需要的仿真内容。而且除了电芯片,因为5G通信的火热,光通信也是目前的热点行业,也通过光器件的仿真教会大家如何做光器件的仿真。时长35个小时,且不断加餐中,并建立了订阅用户交流群和答疑专栏服务等,获得了一大批订阅用户的好评。

从我的经历可以看出,虽然我是机械专业毕业,但也并不是无法掌握电磁场仿真,原因就是在我看来都是求解偏微分仿真,只要把那几本书看透了,用软件熟练即可。另外还有一种思想,就是每一次仿真都是做工程,当然这个仿真工程和实际问题是两条线,能否让其相交就要看工程师自己的咯,欢迎联系平台加入芯片仿真行业用户交流群。

从此掌握Icepak、Mechanical和HFSS芯片封装仿真应用

PSpice电路仿真攻略-AD637高精度有效值转换芯片模型为例