信号完整性测试,关于SMA装配的细节,很多人都忽视了

本文摘要(由AI生成):

本文总结了SMA转接头的应用及其在不同速率下的带宽需求,特别强调了在高速率时代,SMA转接头和PCB板边铺铜的细节对信号完整性的影响。通过实际测试和仿真分析,揭示了SMA pin处阻抗不连续性的原因,并提出了优化措施。文章还指出,在低速时代这些问题可能被忽视,但随着速率的提升,这些问题将变得显著。文章最后提供了仿真的一些说明和注意事项,供读者参考。

SMA转接头是射频微波、天线和高速电路测试经常用到的一种连接器,应用非常广泛,种类也很多。在信号完整性的测试夹具中,2.92mm的SMA用的较多,它的带宽可以到40GHz,对于25Gbps的速率来讲,完全够用,如果速率更高,就得选用带宽更高的2.4mm或者1.85mm的SMA转接头。

或许就是因为经常用,关于SMA装配的细节,很多人都忽视了,毕竟在2.5Gbps和10Gbps时代,测试夹具设计只要不是很离谱的设计,稍微注意下高速信号的处理,测试出来的性能都不会差。

但是到了100Gbps(4*25Gbps)或者更高速率时代,设计测试夹具,就不能那么马虎了,尤其是对于高速信号出入的门户SMA转接头,更要特别注意。

先来看两张实际测试的SMA的TDR曲线图,单独看SMA的TDR,保持末端开路,阻抗一致性比较好,稍微偏感性,最大阻抗为51.3ohm,此时如果将SMA安装到PCB板上,问题就来了,竟然有一个63.9ohm的阻抗尖峰,这是怎么回事?跟仿真是完全对应不上的,SMA pin处是一个典型的阻抗不连续性结构,在仿真时肯定会重点照顾这里。

SMA末端开路TDR分布

SMA安装在PCB上的阻抗分布

仿真TDR

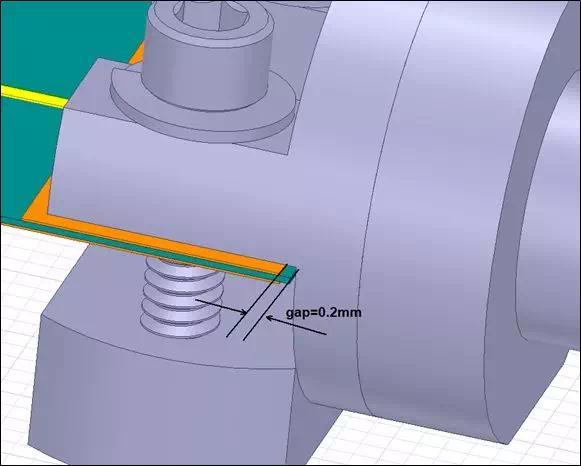

后来仔细观察PCB,发现了一个常见却不重视的细节,那就是PCB的板边控制,PCB的板边铺铜一般会保留至少0.2mm的安全间距,常见的是保留0.2mm~0.5mm,就是因为这个安全间距,导致了SMA pin处的阻抗偏高。

PCB板边控制

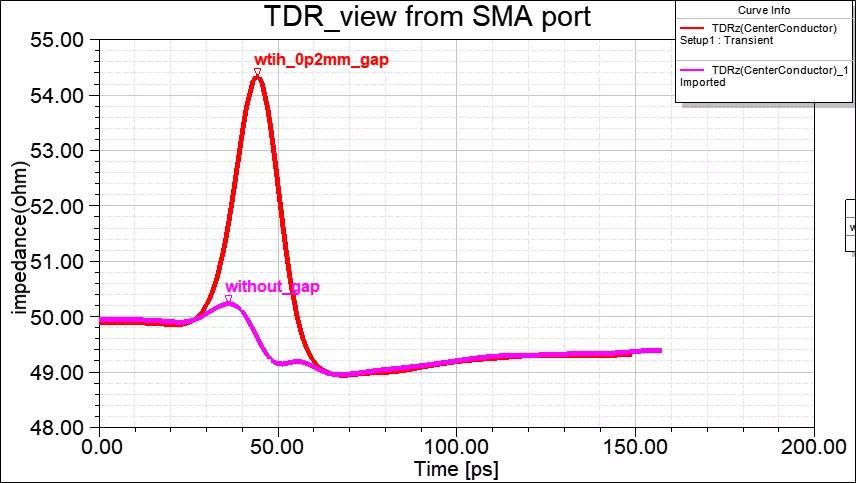

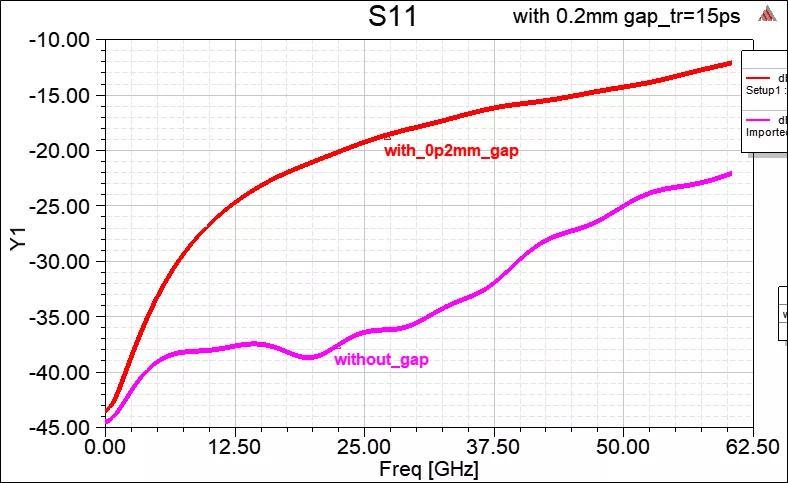

既然找到一个重大疑点,就先来仿真看看是否会重现结果,果然,如果将铜内缩0.2mm,pin处的阻抗会偏高至54.3ohm,如果内缩0.4mm,那么仿真阻抗也会到65.48ohm,跟实际测试的现象很一致,因此到了25Gbps这么高的速率,PCB铺铜一定要到板边,不然就会在SMA pin这里出现很大的反射,见下图的S11。

铺铜内缩0.2mm model

铺铜内缩0.2mm跟铺铜到板边TDR对比

铺铜内缩0.4mm 仿真TDR

反射对比

后面查找了一些资料,发现SMA厂家推荐的也是铺铜到板边,不能留有任何间隙,铺铜没到板边,就是相当于留了间隙,so gap causes poor connection at higher frequency。

SMA厂家推荐无间隙

留有间隙将导致高频性能变差

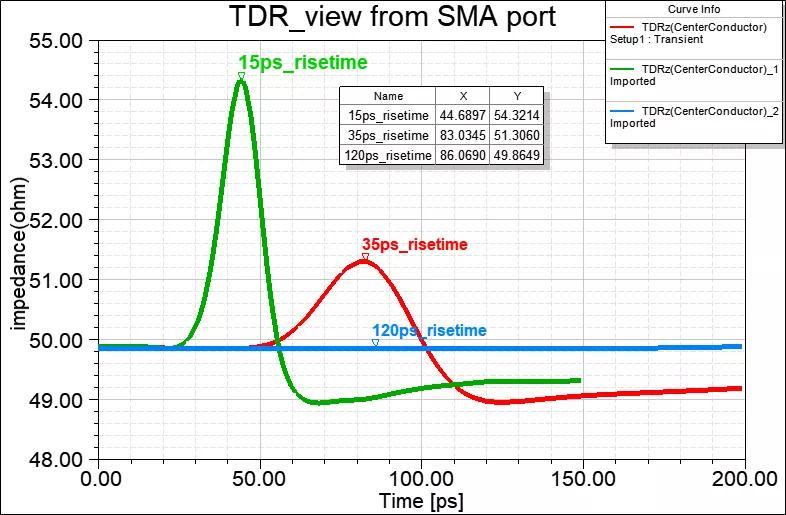

为什么这个铺铜没到板边,不会被注意呢,那是因为在低速(10Gbps及其以下速率)时代,这样用根本就不会有问题,这跟信号的上升沿时间有关系,来看一张仿真的TDR曲线。

同样的一小段传输线结构,一个2.92mm的SMA加一小段50ohm微带线,覆铜距离板边内缩0.2mm,在不同的信号上升沿时间下观察TDR,可以看到,对于120ps(2.5Gbps)的rise time,差不多就是标准的50ohm传输线,而当rise time为35ps(10Gbps)时,稍微表现为感性,SMA pin处的阻抗偏高为51.3ohm,如果继续提高rise time为15ps(25Gbps),那么pin针这里的阻抗会偏高至54.3ohm,已经超出了50ohm+/-2.5%的范围了,将会导致较大的反射,也就是速率提高了,才会出现问题。

SMA和微带线model

不同上升沿时间下TDR对比

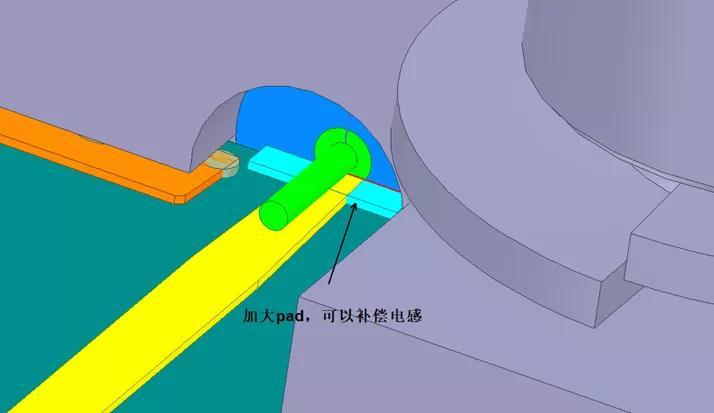

除了铺铜至板边,还有其他优化SMA pin处阻抗的办法吗?也是有的,可以加大pad,参考下图,具体加大尺寸要根据你选择的SMA封装以及层叠来定,需要经过严格的仿真优化,才能得到合适的尺寸。

加大pad,补偿电感

补偿后TDR对比图

以上即是SMA仿真和测试时应该注意的事项,一点经验,供大家参考。

下面附上仿真的一些说明,求解方式使用的时hfss transient,有两个地方请大家注意下:

作者:萧隐君 仿真秀科普作者,ANSYS Electronics Desktop痴迷者,擅长光模块光器件信号完整性仿真与设计,整机EMC电磁兼容仿真。

声明:原创文章,首发仿真秀公 众号(ID:fangzhenxiu2018),部分图片源自网络,如有不当请联系我们,欢迎分享,禁止私自转载,转载请联系我们。

获赞 10680粉丝 22148文章 3746课程 232