封装寄生参数对400G FR4 ROSA OE带宽的影响

本文的仿真结果基于下面住友写的论文,感兴趣的可以去网上下载这篇文章。

文章的大体意思是:TIA输入端的封装,下图红圈部分,也就是打线的寄生电感和PD submount的寄生电容会导致OE传输参数上的谐振,谐振对性能有两个影响,一是降低带宽;二是增大通道间的串扰。

这个谐振很难消除,只能将这个谐振推到高频,推到带宽之外,文章提出了在PD的cathode并联电容的做法,可以将该谐振从41GHz推到70GHz,参考下面的原理图,红色虚线部分既是引入的并联LC电路。

上图中Lwire是PD阴极的打线电感,电感值为0.3nH,Ct是PD阴极封装的对地电容,容值为50fF,这个LC将会在41GHz导致OE传输参数的谐振。

如果在PD的阴极通过打线并联一个100pf(Cb)的电容,并控制打线电感为0.16nH(Lb),这个谐振可以推向70GHz。

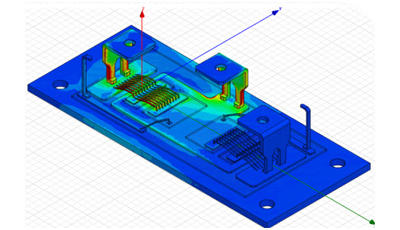

为了验证上面的结论,搭建了一个ROSA小信号电路模型进行AC simulation,是一个纯电路模型,没有用到HFSS提取S参数,电路图如下:部分电路用青蛙遮挡,避免被警告,红色虚线框既是额外的并联LC电路。

仿真结果显示,没有Lb和Cb的并联电路(红色曲线),在41GHz有个很深的谐振,当加上Lb和Cb的并联电路后(蓝色曲线),谐振推到了70GHz,而且带宽也增大了,带内平坦度也改善了,完全符合论文的结果,大写的佩服!

不过关于这篇论文,我也有疑问,文章中实测的OE曲线并没有看到明显的谐振,而仿真有很大的谐振,这就是仿真和实测的差异了,值得继续研究!

声明:原创文章,欢迎留言与我讨论,如需转载留言

登录后免费查看全文

著作权归作者所有,欢迎分享,未经许可,不得转载

首次发布时间:2021-05-03

最近编辑:3年前

相关推荐

最新文章

热门文章