SI-list【中国】PCIE 4.0 CLBTest Fixture

本文摘要(由AI生成):

迪赛康PCIE 4.0 CLB测试夹具支持PCIE1.0~4.0数据测试,包括X1,X4,X8,X16金手指接口,采用SMP高速连接器与仪器连接,支持PCIE1.0~4.0的多种码型切换和码型显示,机械尺寸为PCIE板卡标准半长全高尺寸167.55mm*111.15mm。单板尺寸均满足PCIE标准板卡的半长全高尺寸,PCIE信号全部走微带线,无打孔,阻抗设计控制差分85欧姆,包含1倍和2倍校准线。采用高速SMP接头与仪器连接(最大带宽支持60Ghz)。经测试,两款CLB单板阻抗均在85Ω±5%范围内。

应用场景:

支持全带宽PCIE4.0基板测试(向下兼容)

主要特点

阻抗一致性优越,差分阻抗85Ω±5%。

极低的插入损耗。

各通道skew差异小于±2ps。

SI性能优化至16Gbps,符合PCIE4.0协议。

高性能SMP连接器,最大带宽支持到60Ghz。

自动码型切换,测试码型实时显示。

产品描述

迪赛康PCIE 4.0 CLB(Compliance Load Board)测试夹具支持PCIE1.0~4.0数据测试,包括X1,X4,X8,X16金手指接口。单板采用SMP高速连接器与仪器连接,并支持PCIE1.0~4.0的多种码型切换和码型显示。机械尺寸为PCIE板卡标准半长全高尺寸167.55mm*111.15mm。

2.产品设计

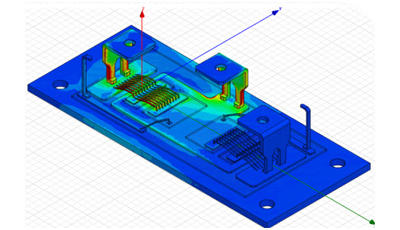

PCIE 4.0 CLB测试单板主要用来测试系统的主板PCIE接口,边缘分别是X1,X4,X8,X16的金手指,主要是插在主板对应槽位的PCIE插槽上,从测试仪器通道引出的SMP线缆接至CLB上的对应测试点。

基于板卡尺寸限制,我们将4种金手指设计在2块单板上,一块上面集成X1和X16接口,另一块集成X4和X8接口。

单板尺寸均满足PCIE标准板卡的半长全高尺寸,PCIE信号全部走微带线,无打孔,阻抗设计控制差分85欧姆,包含1倍和2倍校准线。采用高速SMP接头与仪器连接(最大带宽支持60Ghz)。

CLB单板可以在测试中通过按钮自动切换码型,支持从PCIE1.0到PCIE4.0的多种码型切换,还可以调整和随时复位码型,双方向对称显示。

3. 产品测试

测试仪器:KEYSIGHT 网络分析仪 E5071C(300khz—20Ghz)

通过同轴线缆和SMP转接线连接单板校准线,测试单板实际差分阻抗

经测试,两款CLB单板阻抗均在85Ω±5%范围内。

通过同轴线缆和SMP转接线连接单板校准线,测试回波损耗和插入损耗

声明:原创文章,欢迎留言与我讨论,如需转载留言