4步教会你使用Sherlock的ICT测试模块对电路板进行过应力仿真

以下文章来源于上海安世亚太 ,作者李桂花

ICT技术已经是现代电子企业常用的测试技术,使用ANSYS Sherlock软件进行ICT测试,评估由于过应力导致的风险组件,并根据结果提出改进措施。

随着微电子技术和电子组装技术的发展,PCBA(Printed Circuit Board Assembly,印刷电路板组件)布局和组装呈现出复杂化的趋势。PCB中的器件尺寸微型化、引脚间距紧凑化都使得 PCBA在极大程度上增大了产品失效的可能性。

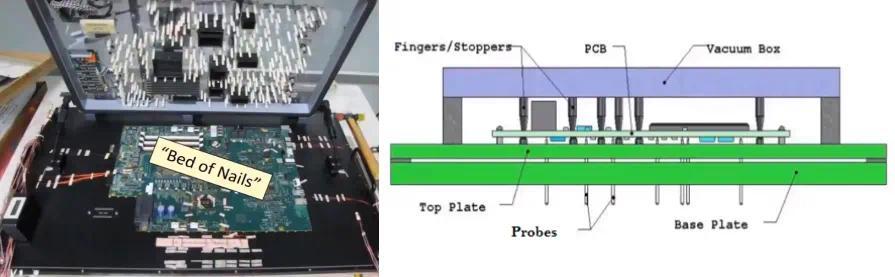

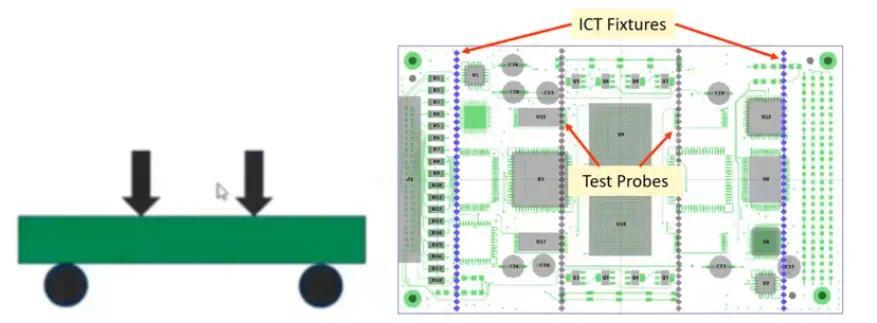

它使用一系列测试探针和测试夹具,在一个电路板的一面或两面来测试制造过程中的电气连接。每个测试探针施加一个力在一个特定的电路板位置,称为测试点,由设计确定。在测试过程中,所有这些测试点力的联合作用使电路板产生弯曲,如果应力值足够高,焊点可能会失效,PCB板上的元件也将产生超过允许范围的应力。

图1 ICT测试仪

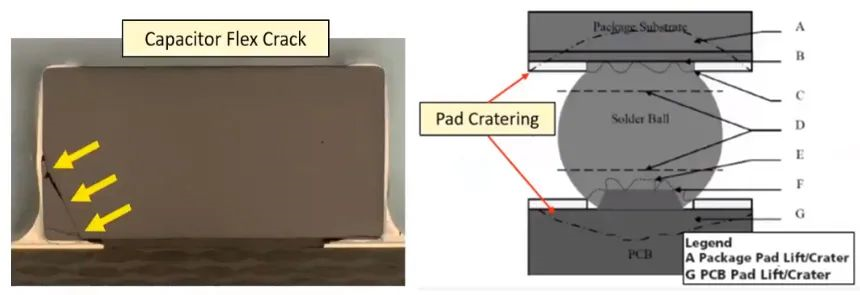

图2 电路板常见的失效模式:陶瓷电容器的弯曲开裂、垫坑

为了提前避免失误和发现问题,在生产过程中需要对ICT步骤进行应力应变测量并监控,以确定产品应力应变处于允许范围内。如果测量值超过了电路板允许的应力应变水平的最大值,将对电路板进行重新布局设计或者调整夹具设计,或者按要求改变流程,使得应力应变数值回到允许范围之内。

02ANSYS Sherlock

第一步

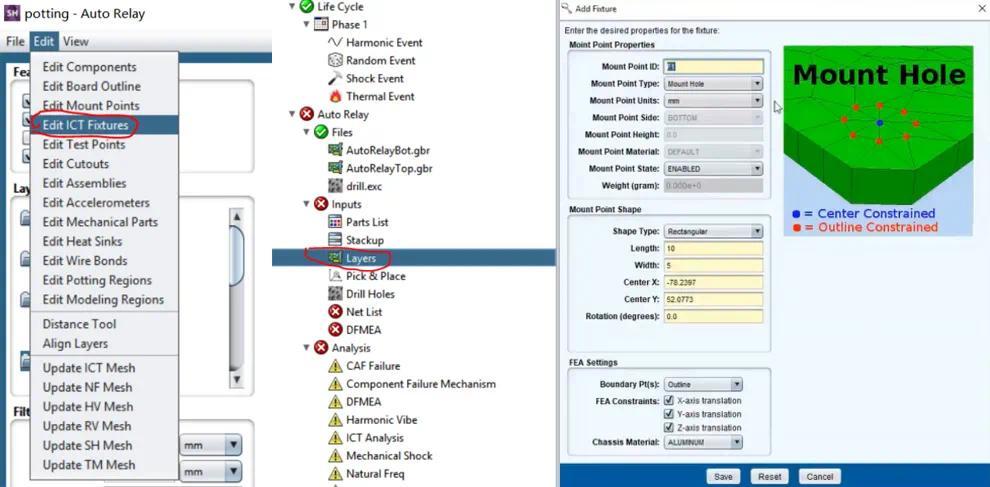

进入PCB的layer层,定义电路板测试的约束条件。如固定孔约束、支撑约束等,约束条件可以复制也可以通过文件导入。

图3 增加测试约束条件

图4 约束条件可以复制

第二步

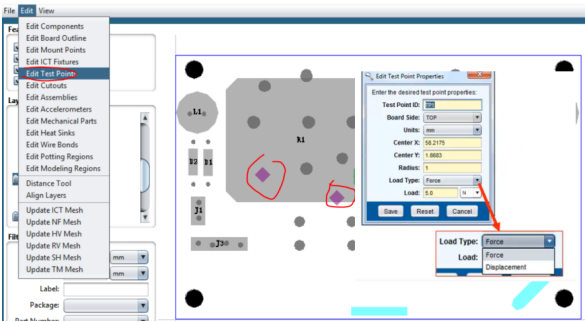

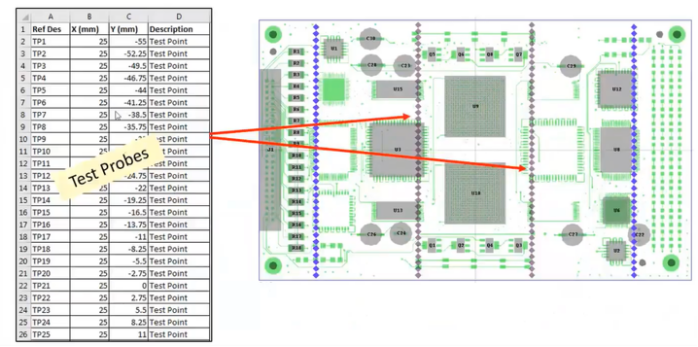

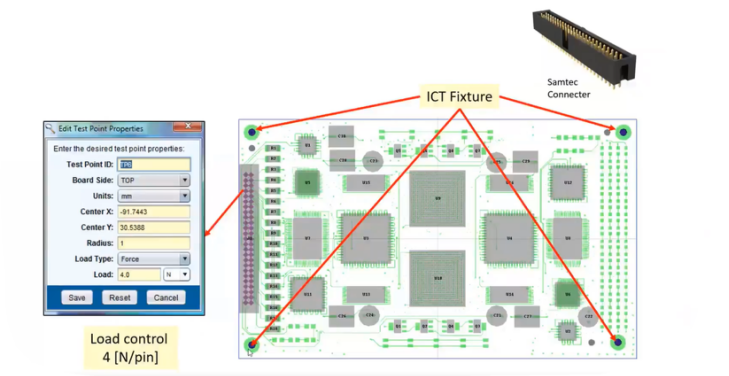

增加ICT测试点,并定义测试点载荷(力或者位移)。简单的测试点可以根据坐标系手动一个一个加入,如果测试点非常多,可以通过文件导入的形式输入。

图5 手动增加单个测试点

图6 复杂测试点可通过文本文件导入

第三步

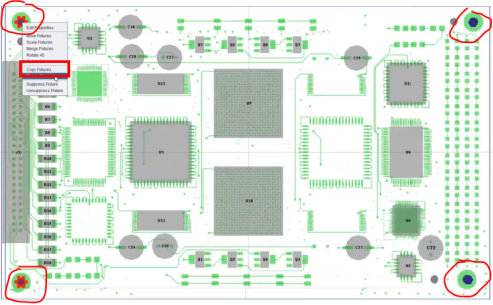

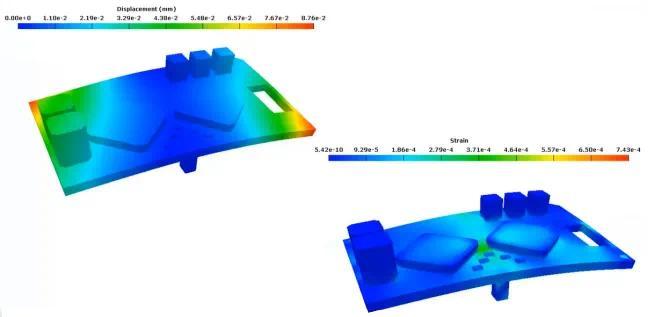

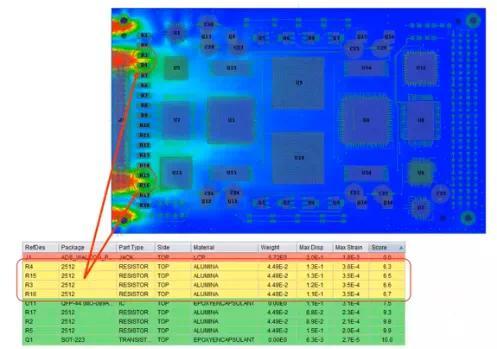

求解并查看结果,评估由于过应力导致的风险组件。

图7 电路板三维位移和应变结果

图8 电路板危险组件按照分数不同颜色显示

第四步

在上述分析结果基础上,提出改进措施。例如,通过改变测试点位置,减少测试点载荷/位移,增加或移动板支撑,填充灌封胶等方法在Sherlock软件里对电路板设计进行快速迭代设计,以期达到产品测试合格的目标。

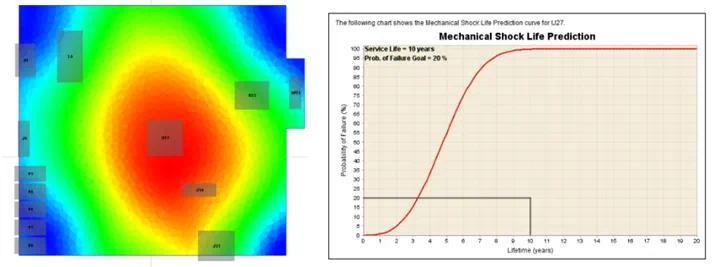

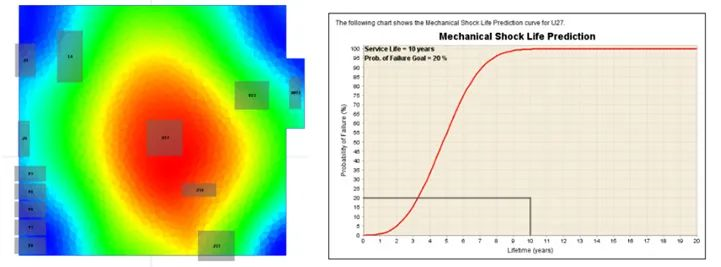

例如在下图中,软件分别通过移动高风险区域的组件U27到合适的位置(10年内失效率大于20%)、增加约束条件(10年内失效率约为5%,达到设计目标)、填充灌封胶(失效率非常低,达到设计目标)的方法来降低产品的失效率。

图9 初始产品设计的失效率(2年内达到5%)

图 10 移动组件U27到合适的位置、增加约束条件、

填充灌封胶降低失效率

03应用扩展

除了ICT测试过程外,类似活动包括四点弯曲测试、电路板子卡或连接器插入过程、分板过程、散热器连接、对电路板的不适当支撑等都会引起电路板过应力失效,这些也可以通过Sherlock的ICT测试模块进行仿真。

图11 四点弯曲试验及ICT实现

图 12 直插连接器对电路板影响及ICT实现